Dengan peningkatan kerumitan reka bentuk PCB, bekalan kuasa yang stabil dan boleh dipercayai telah menjadi arah aliran baharu dalam penyelidikan mengenaireka bentuk PCB berkelajuan tinggi. Terutama apabila bilangan komponen pensuisan terus meningkat dan Vcore terus menurun, turun naik kuasa cenderung membawa pengaruh yang mematikan kepada sistem. Oleh itu, mengekalkan kestabilan sistem kuasa telah menjadi titik utama dalam reka bentuk PCB berkelajuan tinggi.

Walau bagaimanapun, disebabkan kewujudan impedans sistem kuasa, kejatuhan voltan yang agak besar dijana oleh arus peralihan beban dalam impedans sistem kuasa, yang membawa kepada ketidakstabilan sistem. Untuk memastikan kuasa normal dibekalkan kepada setiap komponen dari awal hingga akhir, impedans dalam sistem kuasa perlu dikawal, yang bermaksud impedans tersebut harus dikurangkan sebanyak mungkin.

Penggunaan kapasitor nyahganding ialah cara yang berkesan untuk mengekang impedans dalam sistem kuasa. Artikel ini menganalisis punca larangan impedans dalam sistem kuasa melalui kapasitor nyahganding dan menyenaraikan kaedah dari segi pemilihan kapasitor nyahganding. Selain itu, ia terutamanya mengkaji cara menentukan kedudukan kapasitor nyahganding berdasarkan analisis harmonik untuk memaksimumkan larangan impedans dalam sistem kuasa.

Analisis Impedans

Kuasa dan tanah boleh dianggap sebagai kapasitor plat besar yang kapasitinya dikira berdasarkan formulaC=kAr/d

Dalam formula ini,kialah 0.2249 inci;Amerujuk kepada kawasan selari antara dua satah;rmerujuk kepada pemalar dielektrik medium dan nilainya ialah 4.5 bagi bahan papan FR4 yang biasa digunakan;dmerujuk kepada jarak antara kuasa dan tanah. Sebuah PCB bersaiz 2x1 inci diambil sebagai contoh. Kapasitans kapasitor yang dibentuk oleh kuasa dan tanah dengan kawasan selari 20 mil adalah lebih kurang 0.2249x4.5x2x1/0.02=101.2pF. Berdasarkan formula ini, dapat ditunjukkan bahawa kapasitans nyahganding dalam sistem kuasa adalah sangat kecil sehingga impedans yang sepadan akan menjadi sangat besar, biasanya beberapa ohm. Oleh itu, ia jauh daripada mencukupi untuk mengurangkan impedans melalui nyahganding kendiri dalam sistem kuasa.

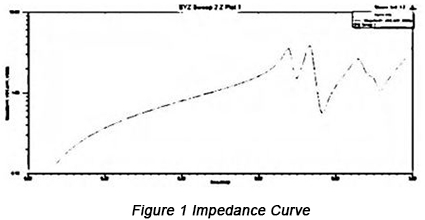

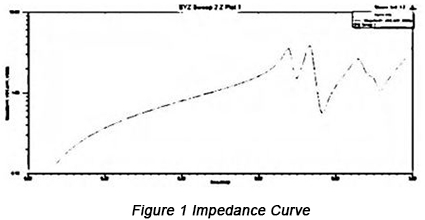

Alat simulasi SIWAVE pada tahap 2.5D digunakan untuk melaksanakan simulasi impedans pada peranti aktif. Rangkaian kuasa dan tanah U41 dipilih untuk mengira parameter XYZ dengan julat imbasan dari 0 hingga 1GHz, melalui mana lengkung impedans diperoleh seperti dalam Rajah 1 di bawah.

Dalam rajah tersebut, dapat dilihat bahawa lengkung impedans berubah dengan perubahan frekuensi dan impedans berubah dengan ketara pada titik lengkok pada nilai 670MHz, 730MHz dan 870MHz.

Kaedah Larangan

• Analisis teori tentang larangan impedans oleh kapasitor nyahganding

Oleh kerana mustahil untuk mengurangkan impedans melalui nyahgandingan daripada kuasa itu sendiri, kapasitor nyahganding perlu digunakan untuk menghalang impedans.

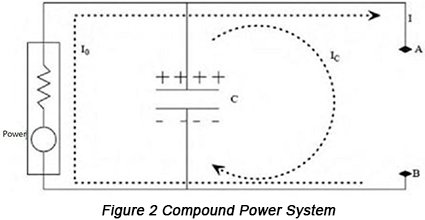

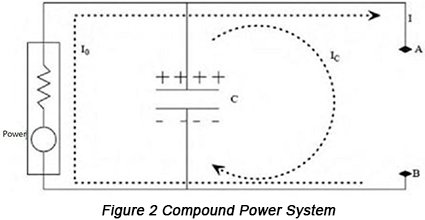

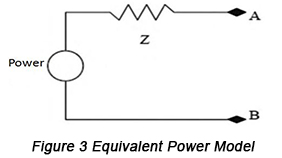

Rajah 2 ialah rajah sistem kuasa sebatian. Rajah 3 menunjukkan sistem kuasa ini dalam model kuasa setara.

Satu formula boleh digunakan untuk mewakili litar ini:V=ZxL. Satu keadaan harus dicapai di mana walaupun arus transien beban mengekalkan perubahan besar antara titik A dan titik B, perubahan voltan mestilah sangat kecil antara kedua-dua titik tersebut. Berdasarkan formula, matlamat ini tidak akan dapat dicapai melainkan nilai impedans (Z) adalah cukup kecil. Dalam Rajah 3, penggunaan kapasitor nyahganding adalah membantu dalam pelaksanaan matlamat ini sehingga dapat ditunjukkan bahawa kapasitor nyahganding berupaya mengurangkan impedans dalam sistem kuasa dari perspektif kesetaraan. Selain itu, dari perspektif prinsip litar, kesimpulan yang sama dapat dikekalkan. Kapasitor mempunyai impedans yang rendah terhadap isyarat arus ulang-alik. Oleh itu, penglibatan kapasitor sebenarnya pasti akan mengurangkan impedans arus ulang-alik dalam sistem kuasa.

• Pemilihan kapasitans kapasitor nyahganding

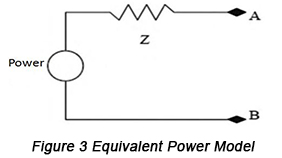

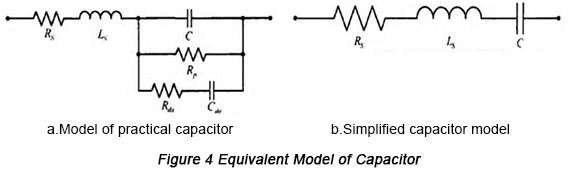

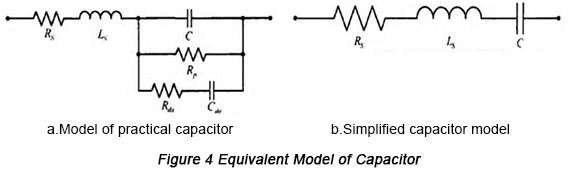

Tidak pernah wujud kapasitor yang ideal, ia sentiasa mempunyai parameter parasit. Pengaruh terbesar terhadap prestasi frekuensi tinggi kapasitor berpunca daripada ESR (Rintangan Siri Berkesan) dan ESL (Induktans Siri Berkesan). Rajah 4 menunjukkan model setara dengan mengambil kira parameter parasit.

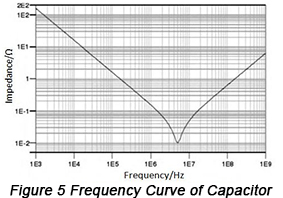

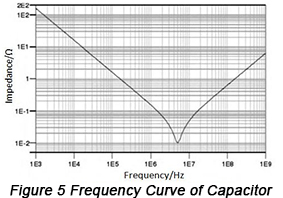

Kapasitor juga boleh dianggap sebagai litar harmonik siri dengan frekuensi harmonik siri yang mengikut formula:f=1/2PIFC. Apabila ia berada dalam keadaan frekuensi rendah, ia memaparkan sifat kapasitans. Namun, apabila frekuensi meningkat, ia sentiasa memaparkan sifat induktansnya. Dengan kata lain, impedansnya akan meningkat terlebih dahulu dan kemudian berkurang dengan peningkatan frekuensi dan nilai minimum impedans setara berlaku pada frekuensi harmonik siri.f0. Pada ketika ini, reaktans kapasitif dan reaktans induktif saling mengimbangi dengan tepat, menunjukkan kesetaraan antara nilai impedans dan ESR dengan rintangan setara terkecil bagi kapasitor. Lengkung frekuensi kapasitor ditunjukkan dalam Rajah 5.

Oleh itu, dalam proses pemilihan kapasitor, titik frekuensi harmonik kapasitor yang dipilih terletak bersebelahan dengan titik frekuensi yang akan mengalami nyahgandingan. Prestasi kapasitifnya perlu digunakan sepenuhnya sebelum mencapai frekuensi harmonik kendiri sedapat mungkin.

Kapasitor berbeza dengan kapasitans berbeza yang serasi dengan frekuensi harmonik kendiri berbeza dipaparkan dalam jadual di bawah.

|

Kapasitans

|

DIP (MHz)

|

STM (MHz)

|

| 1.0μF |

2.5 |

5 |

| 0.1μF |

8 |

16 |

| 0.01μF |

25 |

50 |

| 1000pF |

80 |

160 |

| 100pF |

250 |

500 |

| 10pF |

800 |

1.6(GHz) |

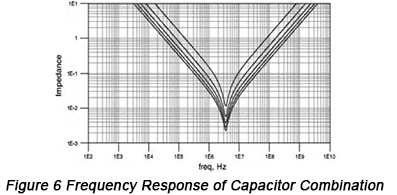

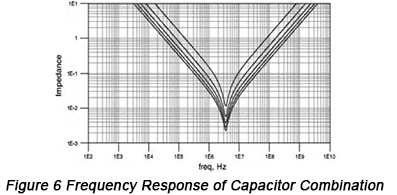

Secara umumnya, sifat harmonik bagi kapasitor nyahganding diperlukan untuk digunakan dan impedans masukan terendah diperoleh melalui gabungan selari kapasitor. Respons frekuensi selari bagi kapasitor jenis yang sama digambarkan dalam Rajah 6 di bawah.

Berdasarkan kaedah ini, ESR dan ESL setara dapat dikurangkan dengan ketara. Untuk berbilang kapasitor (n) dengan kapasitans yang sama, kapasitans setara C menjadi nC selepas digabungkan manakala induktans setaraLmenjadiL/n, ESR bersamaan menjadi R/n. Walau bagaimanapun, frekuensi harmonik kekal tidak berubah. Dapat dilihat bahawa memandangkan frekuensi harmonik kendiri adalah sama bagi jenis kapasitor yang berbeza, lebih banyak kapasitor selari digunakan, lebih kecil impedans dalam kawasan kapasitif dan induktif, dengan titik frekuensi harmonik kendiri tidak berubah.

Kesimpulannya, dalam proses pemilihan kapasitor nyahganding, frekuensi nyahganding harus dianggap sebagai titik frekuensi harmonik kendiri nyahganding supaya kapasitor yang sepadan dapat dipilih. Di samping itu, penggunaan selari berbilang kapasitor dengan nilai kapasitans yang sama mampu meningkatkan keupayaan nyahganding dan mengurangkan impedans.

• Penentuan kedudukan kapasitor nyahganding

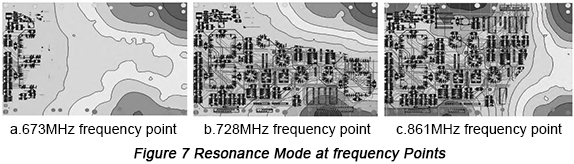

Selepas pemilihan kapasitor nyahganding, kedudukan kapasitor tersebut perlu diambil kira. Satah kuasa dan satah bumi boleh dianggap sebagai rangkaian yang terdiri daripada berbilang induktor dan kapasitor atau sebagai rongga resonan. Pada frekuensi tertentu, resonans berlaku pada induktor dan kapasitor, mempengaruhi impedans dalam sistem kuasa. Dengan peningkatan frekuensi, impedans berubah secara berterusan terutamanya apabila resonans selari kekal ketara, impedans turut meningkat dengan ketara. Oleh itu, kedudukan khusus kapasitor nyahganding perlu dipastikan bersama-sama dengan analisis harmonik PCB.

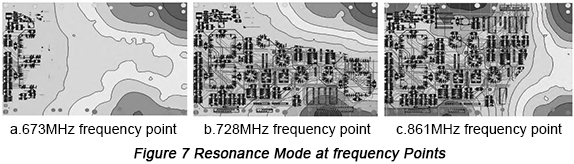

Dengan menggunakan fungsi analisis resonans alat simulasi SIWAVE, parameter setara seperti rintangan, kapasitans dan induktans diperoleh. Selain itu, analisis resonans PCB perlu dilaksanakan dengan mod resonans pada titik frekuensi berbeza yang diperoleh, seperti yang ditunjukkan dalam Rajah 7.

Digabungkan dengan Rajah 1, dapat diperhatikan bahawa beberapa titik frekuensi dengan impedans yang agak besar adalah sepadan dengan titik frekuensi di mana resonans dijana. Oleh itu, berdasarkan hasil analisis resonans, dapat disimpulkan bahawa di kawasan dengan resonans yang serius, kapasitor nyahganding dengan nilai kapasitans yang sesuai harus diletakkan bagi mengurangkan impedans.

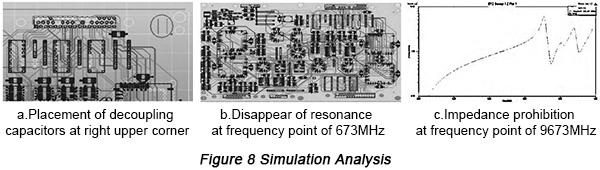

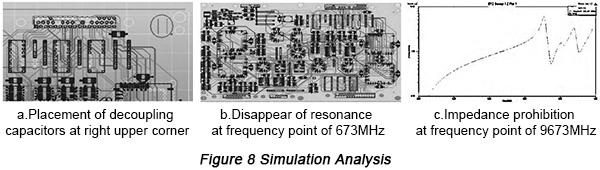

Ambil titik frekuensi 673MHz sebagai contoh, kapasitor nyahganding boleh diletakkan secara selari supaya resonans akan hilang dan impedans yang sepadan akan dihalang, seperti yang ditunjukkan dalam Rajah 8.

Berdasarkan analisis resonans PCB, kedudukan sepadan di mana resonans berlaku boleh ditentukan, dan berdasarkan kedudukan tersebut, kapasitor dengan saiz yang sesuai diletakkan secara selari untuk menghalang impedans.