PCB ถูกเพิ่มไปยังตะกร้าสินค้าของคุณเรียบร้อยแล้ว

อิทธิพลของการจัดวางแผงวงจรพิมพ์ (PCB Layout) ต่อสมรรถนะ EMC ของผลิตภัณฑ์อิเล็กทรอนิกส์

• อิทธิพลของการรบกวนโค้ดร่วมต่อสัญญาณภายใน PCB

เส้นลายพิมพ์ด้านในของแผงวงจรพิมพ์ (PCB) มีพารามิเตอร์寄生เมื่อเทียบกับแผ่นกราวด์อ้างอิง และเมื่อมีการส่งสัญญาณฟังก์ชันภายใน PCB โหนดศักย์ไฟฟ้าเท่ากันเดียวกันในเครือข่ายเดียวกันในวงจรจะไม่คงศักย์เท่ากันอีกต่อไป กระแสไฟฟ้าฉันภายในแผงวงจรพิมพ์ (PCB) เริ่มต้นจากปลายต้นทาง ผ่านตัวนำสัญญาณหลายตัวแล้วกลับไปยังแหล่งสัญญาณ ก่อให้เกิดสัญญาณขึ้น นอกจากนี้ฉันมักจะไหลไปตามเส้นทางที่มีอิมพีแดนซ์ต่ำเพื่อให้ฉันมักคงสภาพไม่เปลี่ยนแปลงด้วยความเสถียรของอิมพีแดนซ์

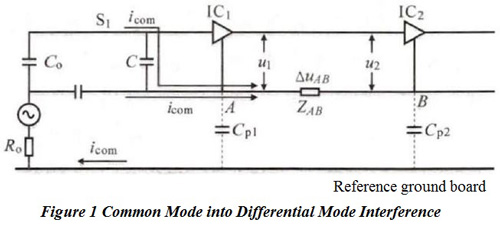

รูปที่ 1 แสดงให้เห็นกระบวนการที่สัญญาณรบกวนโหมดร่วมถูกแปลงเป็นสัญญาณรบกวนโหมดดิฟเฟอเรนเชียลภายในแผงวงจรพิมพ์ (PCB) ฉันdหมายถึงกระแสโหมดดิฟเฟอเรนเชียลที่ไหลอยู่ภายใน PCB ขณะที่ฉันcomหมายถึงกระแสโหมดร่วมที่เริ่มต้นจากภายนอกแผงวงจรพิมพ์ (PCB) และไหลเข้าสู่แผงวงจรพิมพ์ผ่านแผ่นกราวด์อ้างอิง หรือเริ่มต้นจากภายในแผงวงจรพิมพ์และไหลกลับเข้าสู่ภายในแผงวงจรพิมพ์ผ่านแผ่นกราวด์อ้างอิง ความถี่สูงฉันcomมีสองเส้นทาง: เส้นทางแรกคือจากจุดAชี้Bภายในแผงวงจรพิมพ์เริ่มจาก GND; ส่วนที่สองคือจากจุดAชี้Bเริ่มจากพอร์ต S1ไปยังแผงวงจรพิมพ์ (PCB) ภายในผ่านค่าความจุไฟฟ้า C. อิมพีแดนซ์กราวด์ZABนำไปสู่การเกิดของ Δuเอบีดังนั้นเมื่อสัญญาณปกติถูกส่งไปยัง IC2การเปลี่ยนรูปจะเกิดขึ้นเพื่อส่งสัญญาณ และสัญญาณรบกวนโหมดร่วมจะถูกแปลงเป็นสัญญาณรบกวนโหมดดิฟเฟอเรนเชียล ซึ่งก่อให้เกิดผลกระทบต่อสัญญาณปกติตามสมการที่u2=ยู1-ΔuAB.

ดังนั้น ทันทีที่ฉันcomเข้าสู่ภายในแผ่น PCB ผ่านพอร์ต I/O หรือการแผ่รังสีในอากาศ ตัวเก็บประจุกรองโหมดดิฟเฟอเรนเชียลบนสายสัญญาณของ PCB สามารถเพียงกดให้สัญญาณรบกวนบายพาสลงสู่ GND เงื่อนไขเบื้องต้นของผลลัพธ์นี้คือ GND ถูกมองว่าเป็นอิมพีแดนซ์ต่ำสำหรับกระแสย้อนกลับของสัญญาณ และกระแสจะไหลไปในทิศทางของอิมพีแดนซ์ต่ำเสมอ

• กุญแจสำคัญของการออกแบบ EMC ในการใช้งานจริง: อิมพีแดนซ์กราวด์ใน PCB

สาเหตุของการเกิด EMC จากสัญญาณความถี่สูงอยู่ที่ระดับอ้างอิงสัญญาณ GND ไม่สามารถคงคุณลักษณะของอิมพีแดนซ์ต่ำไว้ได้ เมื่ออิมพีแดนซ์เพิ่มขึ้นZGNDระดับอ้างอิง คุณภาพของการส่งสัญญาณก็จะลดลงด้วยเช่นกัน เพื่อแก้ปัญหาการรบกวนความถี่สูง วิธีการทั่วไปที่ใช้กันคือการออกแบบ EMCเช่น ฟิลเตอร์ กราวด์ และชิลด์ที่เชื่อมต่ออย่างใกล้ชิดกับ "กราวด์"

ฟิลเตอร์สามารถถือได้ว่าเป็นตัวเก็บประจุลงกราวด์ โดยมีโครงสร้างสองแบบ แบบหนึ่งคือทำให้ตัวเก็บประจุ X ต่อเข้ากับกราวด์อ้างอิงสัญญาณ และอีกแบบหนึ่งคือทำให้สัญญาณต่อเข้ากับเปลือกโลหะด้วยตัวเก็บประจุ Y หรือการต่อกราวด์ที่แตกต่างกันภายใน PCB ชิลด์สามารถถือได้ว่าเป็นผลลัพธ์ของการขยายตัวของกราวด์บน PCB ออกสู่พื้นที่ว่าง วัตถุประสงค์ของฟิลเตอร์หรือชิลด์คือทำให้สัญญาณรบกวนโหมดร่วมความถี่สูงไหลผ่านทางบายพาสที่มีอิมพีแดนซ์ต่ำเพื่อหลีกเลี่ยงไม่ให้ไหลเข้าสู่สัญญาณการทำงานปกติ ในทำนองเดียวกัน วิธีการทั้งหมดนี้จะไม่ทำงานหากกราวด์มีอิมพีแดนซ์ไม่ต่ำ

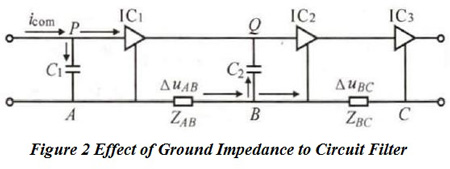

รูปที่ 2 แสดงให้เห็นถึงผลกระทบของอิมพีแดนซ์กราวด์ต่อฟิลเตอร์วงจร ฉันcomไหลตามลำดับของ IC1→ไอซี2→IC1และเมื่อมันไหลไปยังจุดพ,ฉันcomจะไหลเข้าสู่สายย่อยของ IC1และC1ซึ่งเป็นทางที่มันไหลจากจุดAถึงB. หากอิมพีแดนซ์ระหว่างจุดAและBนั่นคือZABมีค่าน้อยกว่ามากเมื่อเทียบกับอิมพีแดนซ์ระหว่างจุดพและ IC1. ในตอนนี้ฉันcomไหลจากจุดพถึงA, IC1สามารถทำให้ฟิลเตอร์เป็นจริงได้ เมื่อฉันcomไหลไปยังจุดBวงจรสาขาจะเกิดขึ้นซึ่งเป็นบ→คและB→ถาม. หากการจัดวางแผงวงจรพิมพ์ (PCB layout) ไม่ได้รับการควบคุมอย่างดี ค่าความต้านทานอิมพีแดนซ์ระหว่างจุดBและCนั่นคือZบีซี,Zบีซี>>ZC2+Zถาม.Zถามหมายถึงอิมพีแดนซ์ระหว่างจุดถามและ IC2.ฉันcomไหลย้อนกลับไปยัง IC2พอร์ตอินพุตผ่านC2เมื่อค่าคาปาซิแตนซ์ที่เดิมถูกใช้เฉพาะสำหรับวงจรรวม (IC)2มีบทบาทในการรบกวนการบุกรุกของสัญญาณ

เพื่อให้ระดับอ้างอิงมีอิมพีแดนซ์ต่ำ โดยทั่วไปมักออกแบบให้เป็นพื้นผิว โดยทั่วไปแล้ว ตัวนำที่มีอัตราส่วนความยาวต่อความกว้างน้อยกว่า 5 สามารถถือได้ว่าเป็นอิมพีแดนซ์ต่ำในทางวิศวกรรม อิมพีแดนซ์ของลายพิมพ์ไม่ได้ถูกกำหนดโดยระดับความยาวหรือความหนาของมัน ในแบบดั้งเดิมหลักการออกแบบ PCBดังนั้น จึงมีการแนะนำอย่างมากให้ใช้การต่อลงกราวด์แบบจุดเดียวสำหรับวงจรแอนะล็อกหลักการออกแบบเลย์เอาต์ PCBการต่อลงกราวด์หลายจุดของวงจรดิจิทัลและการผสมการต่อลงกราวด์ของวงจรโมดูลดิจิทัลไม่สามารถใช้แก้ปัญหา EMC ได้อีกต่อไป

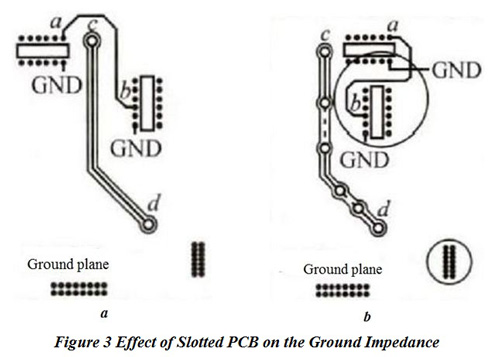

เนื่องจากต้องมั่นใจว่ากระแสย้อนกลับของสัญญาณทั้งหมดมีกราวด์แบบรวมที่มีอิมพีแดนซ์ต่ำ แผ่นวงจร 4 ชั้นหรือหลายชั้นที่มีระนาบกราวด์แบบรวมจึงสามารถตอบสนองความต้องการนี้ได้ ในขณะที่แผ่นวงจรชั้นเดียวแบบต้นทุนต่ำไม่สามารถทำได้ เมื่อจำเป็นต้องใช้แผ่นวงจรสองชั้นเนื่องจากข้อจำกัดด้านต้นทุน ควรออกแบบระนาบกราวด์ที่ค่อนข้างเป็นเนื้อเดียวกันสำหรับสัญญาณภายใน PCB ในการใช้งานจริง อิมพีแดนซ์กราวด์ของ PCB จะได้รับผลกระทบทั้งจากรูปร่างของมันและจากรูผ่านของลวดสัญญาณ รอยแยก และการเซาะร่อง รูปที่ 3a และ 3b แสดงให้เห็นการออกแบบระนาบกราวด์อิมพีแดนซ์ต่ำที่ไม่ดีและดีเยี่ยมตามลำดับ

ในรูปนี้ ส่วนประกอบทั้งหมดอยู่ที่ด้านหน้าของแผงวงจรพิมพ์ ในขณะที่ระนาบกราวด์อยู่ด้านหลัง ชิปเชื่อมต่อกันผ่านลายวงจรพิมพ์abที่ด้านหน้าซีดีมีเส้นพิมพ์อยู่ที่ด้านหลัง ภายใต้แรงกดดันของสัญญาณรบกวนโหมดร่วมความถี่สูงจากภายนอก ร่องที่เกิดจากซีดีจะนำไปสู่การเพิ่มขึ้นของZGNDการไหลย้อนกลับของเส้นพิมพ์ZGNDมีการผันผวนในกระบวนการส่งสัญญาณ ทำให้คุณภาพของสัญญาณต่ำ ดังนั้น ชั้นของเส้นพิมพ์ระหว่างซีดีสามารถแลกเปลี่ยนซ้ำแล้วซ้ำอีกผ่านรูในกระบวนการออกแบบเลย์เอาต์ PCB เพื่อให้ZGNDจะถูกลดลง นอกจากนี้ IC สองตัวSสามารถจัดวางสัญญาณที่ไวต่อการรบกวนไว้รวมกันได้ เพื่อให้ GND กลายเป็นระนาบกราวด์ที่ค่อนข้างเป็นหนึ่งเดียวในบริเวณนั้น เพื่อให้มั่นใจว่าสัญญาณจะไม่ถูกรบกวนในระหว่างกระบวนการส่งสัญญาณ โปรดสังเกตว่าไม่สามารถจัดวางรูผ่านให้มีความหนาแน่นมากเกินไปได้ มิฉะนั้นจะทำให้ระนาบกราวด์เกิดการแตกร้าว ส่งผลให้ระดับของZGND.

การออกแบบการซ้อนชั้นของแผงวงจรพิมพ์ (PCB)

การออกแบบ EMC เหมาะสมที่สุดสำหรับแผ่นวงจรพิมพ์แบบ 4 ชั้น จากมุมมองของ EMS ไม่ว่าจะเป็นโครงสร้างเปลือกโลหะทั้งชิ้นหรือการใช้เปลือกโลหะเพื่อป้องกันวงจรเฉพาะจุดที่มีความไวต่อสัญญาณรบกวน ก็สามารถแก้ปัญหาการรบกวนได้ จากมุมมองของ EMI บางครั้งแผ่นวงจร 4 ชั้นไม่สามารถตอบสนองข้อกำหนดด้านขีดจำกัดการแผ่รังสีได้ และจำเป็นต้องเพิ่มจำนวนชั้น เนื่องจากแผ่นวงจรหลายชั้นสามารถทำให้สัญญาณที่มีความ d สูงu/dtและ dฉัน/dtช่วยให้พื้นที่ลูปสัญญาณมีขนาดเล็กลงในระหว่างกระบวนการส่งสัญญาณ และมอบเส้นทางกระแสย้อนกลับที่มีอิมพีแดนซ์ต่ำสำหรับสัญญาณความเร็วสูง

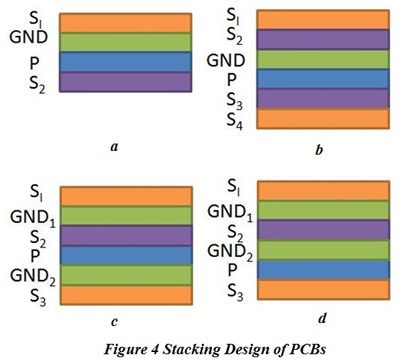

หลักการพื้นฐานของการออกแบบการซ้อนชั้น PCBคือการจัดวางชั้นสัญญาณความเร็วสูงและเพลนจ่ายไฟให้อยู่ติดกับเพลนกราวด์ รูปที่ 4 แสดงการออกแบบการซ้อนชั้นของบอร์ด 4 ชั้นและ 6 ชั้น S1ในรูปที่ 4a หมายถึงชั้นสัญญาณความเร็วสูง ในขณะที่รูปที่ 4b, 4c และ 4d เป็นการออกแบบแผ่นวงจรพิมพ์ 6 ชั้นแบบทั่วไปสามแบบ

ท่ามกลางการออกแบบ PCB แบบ 6 ชั้นทั้ง 3 แบบ การออกแบบบแย่ที่สุดและ S2เลเยอร์ควรเป็นเลเยอร์สัญญาณความเร็วสูง S2เลเยอร์ในการออกแบบคและdเป็นชั้นสัญญาณความเร็วสูง การออกแบบคดีที่สุดเพราะแต่ละชั้นสัญญาณอยู่ติดกับระนาบกราวด์อย่างใกล้ชิดเพื่อให้มั่นใจว่าเส้นทางการไหลกลับของสัญญาณสั้นที่สุดและ S2และชั้น P ถูกป้องกันด้วย GND1และ GND2. เมื่อเทียบกับการออกแบบค, S3ในการออกแบบดอยู่ห่างจากชั้น GND มาก และ P สามารถเกิดได้เพียงเอฟเฟกต์ด้านเดียว แทนที่จะเป็นเอฟเฟกต์สองด้านซึ่งเกิดจากการออกแบบค.

เสาอากาศสมมูลในแผงวงจรพิมพ์ (PCB)

หน้าที่พื้นฐานของเสาอากาศคือการแผ่และรับคลื่นวิทยุไร้สาย ในกระบวนการแผ่รังสี กระแสความถี่สูงสามารถถูกแปลงให้เป็นคลื่นแม่เหล็กไฟฟ้าได้; ในกระบวนการรับ คลื่นแม่เหล็กไฟฟ้าจะถูกแปลงกลับเป็นกระแสความถี่สูง การแผ่รังสีในสาขา EMC โดยหลักแล้วหมายถึงการแผ่รังสีระยะไกล การเกิดขึ้นของเสาอากาศขึ้นอยู่กับเงื่อนไขพื้นฐานสองประการ: แหล่งสัญญาณ RF และตัวนำที่มีความยาวหนึ่ง ๆ ซึ่งต่อเข้ากับแหล่งสัญญาณ RF ในทางวิศวกรรม เชื่อกันว่าจะเกิดเอฟเฟกต์เสาอากาศเมื่อความยาวของตัวนำเป็นไปตามสมการที่ว่าล=λ/20. เมื่อล=(λ/4)นเอฟเฟกต์เสาอากาศมีขนาดใหญ่ที่สุดเมื่อนเป็นจำนวนธรรมชาติ

เมื่อสัญญาณถูกส่งภายในแผ่นวงจรพิมพ์ (PCB) ลูปด้านในจะมีผลเช่นเดียวกับเสาอากาศแบบลูป ยิ่งพื้นที่ลูปมีขนาดใหญ่เท่าใด ผลของเสาอากาศก็จะยิ่งมากขึ้นเท่านั้น การควบคุมลูปของ PCB อย่างเข้มงวดสามารถหยุดการรบกวนแบบโหมดดิฟเฟอเรนเชียลได้อย่างมีประสิทธิภาพ ซึ่งสามารถทำได้จริงในทางปฏิบัติ อย่างไรก็ตาม การเพิ่มความยาวของลายวงจรพิมพ์จะทำให้เกิดผลของเสาอากาศแบบแท่งอย่างชัดเจน ดังนั้นความยาวของสัญญาณเชื่อมต่อจึงควรถูกลดให้สั้นที่สุดเท่าที่จะเป็นไปได้ในกระบวนการจัดวางเลย์เอาต์ PCB

เมื่อค่อนข้างสูงZGNDเกิดขึ้นบนเส้นทางการไหลย้อนกลับของ d สูงu/dตสัญญาณที่ส่งภายในแผงวงจรพิมพ์ (PCB), แหล่งขับโหมดร่วมucomจะจัดขึ้นพร้อมกับฉันcomไหลผ่านZGNDพร้อมด้วยเส้นลายวงจรพิมพ์ที่เชื่อมต่อหรือขั้วต่อ I/O ที่สามารถแผ่รังสีออกสู่ภายนอก

หากแผ่น PCB มีขนาดค่อนข้างเล็ก ลายวงจรด้านในจะไม่สามารถตอบสนองข้อกำหนดการแผ่รังสีของเสาอากาศได้เนื่องจากข้อจำกัดด้านความยาว ภายใต้เงื่อนไขนี้ สายเคเบิล I/O สามารถถือได้ว่าเป็นส่วนขยายของลายวงจรพิมพ์ ซึ่งสามารถตอบสนองข้อกำหนดการแผ่รังสีได้ แม้ว่าไม่มีการเชื่อมต่อโดยตรงกับ I/O ที่เสถียรก็ตาม ก็ควรหยุดการคัปปลิงแบบครอสทอล์กระหว่างสายเคเบิล I/O

การรบกวนข้ามภายในแผงวงจรพิมพ์ (PCB) และวิธีการแก้ไข

• การคัปปลิงระหว่างลายพิมพ์บนแผงวงจรพิมพ์ (PCB) กับกราวด์อ้างอิง

เนื่องจาก EMC มักกล่าวถึงสัญญาณโหมดร่วมความถี่สูงเป็นหลัก พารามิเตอร์แบบกระจายจึงไม่อาจหลีกเลี่ยงได้ทั้งภายในและภายนอก PCB การคัปปลิงแบบความจุไฟฟ้าจะเกิดขึ้นระหว่าง PCB กับกราวด์อ้างอิง ซึ่งค่าความจุแบบกระจายนี้ประกอบด้วยความจุแผ่นและความจุธรรมชาติภายในช่องว่างที่เล็กที่สุด ความจุแผ่นมีสัดส่วนโดยตรงกับขนาดของ PCB และมีสัดส่วนผกผันกับระยะห่างระหว่าง PCB กับกราวด์ ส่วนความจุธรรมชาติภายในช่องว่างที่เล็กที่สุดมีสัดส่วนโดยตรงกับเส้นผ่านศูนย์กลางเทียบเท่าของลายทองแดงภายใน PCB ดังนั้นไม่ว่า PCB จะถูกวางไว้ที่ใด แม้จะอยู่ไกลจากกราวด์อย่างไม่มีที่สิ้นสุด ก็ยังคงมีความจุแบบกระจายระหว่างลายทองแดงภายในกับกราวด์อยู่เสมอ ใน PCB หนึ่งแผ่น ความจุแบบกระจายของระนาบ GND ที่ค่อนข้างเป็นแผ่นรวมตัวกันเมื่อเทียบกับบอร์ดกราวด์อ้างอิงจะมีค่าประมาณ 10pF และความจุแบบกระจายของลายทองแดงภายในเมื่อเทียบกับบอร์ดกราวด์อ้างอิงจะอยู่ในช่วงประมาณ 0.001pF ถึง 0.1pF หรือต่ำกว่านั้น ความจุแบบกระจายของลายทองแดงที่อยู่บริเวณกึ่งกลาง PCB จะต่ำกว่าของลายทองแดงที่ขอบ PCB อย่างมาก

• การคัปปลิงภายในแผงวงจรพิมพ์

a. ทฤษฎีของการคัปปลิงภายในแผ่นวงจรพิมพ์ (PCB) และอิทธิพลต่อสัญญาณ

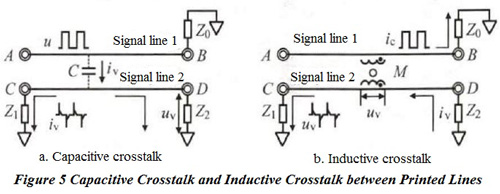

การคัปปลิงภายในแผ่นวงจรพิมพ์ (PCB) ประกอบด้วยการคัปปลิงแบบตัวเก็บประจุและการคัปปลิงแบบตัวเหนี่ยวนำ ซึ่งทฤษฎีของทั้งสองแบบแสดงไว้ในรูปที่ 5

ในรูปนี้ ทั้งสองABและซีดีเป็นเส้นพิมพ์ขนานที่มีช่องว่างเล็ก ๆ ระหว่างสองเส้น Z0หมายถึงตัวนำของสายสัญญาณ 1 ในขณะที่ Z1และ Z2อ้างถึงตัวนำของสายสัญญาณ 2 ตามลำดับ ในรูปที่ 5a เมื่อแรงดันพีคของสัญญาณบนลายพิมพ์เอบีคือu, เวลาขึ้นของสัญญาณคือ Δt และความถี่เชิงมุมคือ ω แรงดันไฟฟ้าของ Z2จะเป็นคุณv=[Z1Z2/(Z1+Z2)]cΔยู/Δtแม้ว่าคมีค่าต่ำมาก ค่า Δu/dtอาจมีค่าสูงมากและไม่สามารถหลีกเลี่ยงผลคูณของมันได้ ในรูปที่ 5b เมื่อกระแสพีคของสัญญาณบนABคือฉันค, เวลาเพิ่มขึ้นของสัญญาณคือ Δตและความถี่เชิงมุมคือ ω ค่าความเหนี่ยวนำร่วมมระหว่างเส้นพิมพ์ 2 เส้นจะผ่านซีดีซึ่งแรงดันไฟฟ้าที่เหนี่ยวนำคือ uv=มωiคแม้ว่ามูลค่าของมมีขนาดเล็กมาก ความถี่สัญญาณจึงอาจเพิ่มขึ้นได้ ดังนั้น ผลคูณของมันจึงไม่อาจหลีกเลี่ยงได้

ดังนั้น การคัปปลิงแบบความจุไฟฟ้าและการคัปปลิงแบบการเหนี่ยวนำจึงเกี่ยวข้องกับพารามิเตอร์กระจายของเส้นพิมพ์ทั้งสองคหรือมระหว่างการออกแบบเลย์เอาต์ PCB ค่าของคและมสามารถลดลงได้โดยการเพิ่มระยะห่างระหว่างเส้นขนาน ในวงจรใช้งานจริง การคัปปลิงแบบตัวเก็บประจุเป็นสาเหตุส่วนใหญ่ในวงจรดิจิทัล และเมื่อระนาบ PCBหากไม่มีความเรียบ ช่องเสียบ หรือรอยร้าว การรบกวนแบบเหนี่ยวนำจะมีอิทธิพลมากกว่าการรบกวนแบบความจุ อย่างไรก็ตาม เมื่อพื้นที่ของ PCB มีจำกัด การรบกวนไม่สามารถจัดการได้ด้วยการเพิ่มระยะห่างระหว่างลายวงจรขนานเพียงอย่างเดียว เพื่อคงพารามิเตอร์กระจายที่น้อยที่สุดระหว่างลายวงจรขนานที่อยู่ติดกัน ควรจัดให้มีการออกแบบระนาบรวมในพื้นที่ฉาย และควรมีชั้นกราวด์ทั้งด้านบนและด้านล่าง

b. อิทธิพลของสายกราวด์ชิลด์ต่อการลดการรบกวนระหว่างสัญญาณ

ระดับของการรบกวนระหว่างสัญญาณถูกกำหนดโดยปัจจัยหลายอย่าง เช่น ความถี่ของสัญญาณ เวลาไต่ระดับขาขึ้นของสัญญาณ ระยะห่างระหว่างเส้นสัญญาณ พอร์ตขับเคลื่อนและคุณลักษณะทางไฟฟ้าของพอร์ตรับ รวมถึงจำนวนชั้นของแผ่นวงจรพิมพ์ (PCB) การรบกวนระหว่างสัญญาณสามารถลดลงได้โดยการวางระนาบกราวด์รวมไว้ใต้เส้นสัญญาณพิมพ์ และสามารถเพิ่มสายกราวด์ป้องกันระหว่างสัญญาณได้

ในกระบวนการออกแบบเลย์เอาต์ PCB มีสองประเด็นที่ช่วยลดการเกิดครอสทอล์กได้ ประการแรก ควรแยกวงจรภายในที่ไวต่อสัญญาณรบกวนออกจากวงจรภายนอก ประการที่สอง ควรป้องกันครอสทอล์กระหว่างวงจรภายในหรือวงจรสัญญาณรบกวนกับสัญญาณอื่น ๆ ในการออกแบบเลย์เอาต์ PCB จริง ควรทำการทดสอบอย่างละเอียดทั้งในเลเยอร์เดียวกันและระหว่างเลเยอร์ต่าง ๆ บน PCB เพื่อให้ตรวจสอบได้ว่ามีความเสี่ยงของการเกิดครอสทอล์กหรือไม่

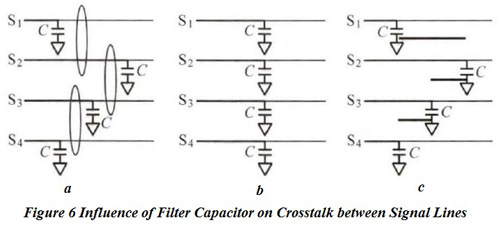

ระหว่างขั้นตอนการออกแบบเลย์เอาต์ PCB สายสัญญาณบางเส้นที่มีคุณสมบัติเดียวกันควรมีการเดินลายที่มีเวลาและทิศทางเดียวกันอย่างหนาแน่น หากข้อจำกัดของพื้นที่บน PCB ทำให้ไม่สามารถวางอุปกรณ์กรองบนเส้นเดียวกันได้ จะมีแนวโน้มทำให้เกิดการครอสทอล์กระหว่างสัญญาณ สถานการณ์นี้แสดงไว้ในรูปที่ 6 ด้านล่าง

c. อิทธิพลของสายดินป้องกันต่อเอฟเฟกต์ขอบ

เมื่อสายสัญญาณที่มีความไวสูงหรือสายสัญญาณที่มีค่า d สูงu/dt, dฉัน/dtถูกจัดเรียงตามขอบ PCB จะมีความเสี่ยงด้าน EMC มากกว่าตัวที่จัดเรียงไว้ตรงกลาง PCB เส้นสัญญาณที่อยู่ใกล้ขอบจะรับสัญญาณรบกวนความถี่สูงหรือการแผ่รังสีจากภายนอกได้ง่ายกว่า เนื่องจากมีค่าคาปาซิแตนซ์ปรสิตที่มากกว่า

ภายใต้ข้อจำกัดของพื้นที่บนแผ่น PCB การจัดวางเลย์เอาต์ PCB ตามหลักการ 20H ในไฟล์ออกแบบนั้นเป็นเรื่องยากมาก สามารถใช้ “แพ็กเก็ต” เพื่อลดการรบกวนและการแผ่รังสีภายนอกได้ เส้นแพ็กเก็ตไม่จำเป็นต้องเป็นไปตามข้อกำหนดเฉพาะ เช่น ความหนาและรูปร่าง โดยปกติเมื่อเส้นสัญญาณอยู่ใกล้ขอบ PCB มากเกินไปจนไม่สามารถปิดทองแดงได้ สามารถเพิ่มเส้นกราวด์ขนาดประมาณ 7 ถึง 10 mils เป็นฉนวนป้องกันได้

d. การรบกวนซึ่งกันและกันระหว่างวงจรดิจิทัลและแอนะล็อก

เมื่อแผงวงจรพิมพ์ (PCB) มีทั้งวงจรดิจิทัลความเร็วสูงและสัญญาณแอนะล็อกระดับต่ำ การรบกวนข้าม (crosstalk) มักจะเกิดขึ้นกับสัญญาณแอนะล็อกจากสัญญาณรบกวนดิจิทัลภายใต้การออกแบบเลย์เอาต์ PCB ที่ไม่ดี การรบกวนซึ่งกันและกันระหว่างวงจรดิจิทัลและแอนะล็อกเกิดจากสาเหตุดังต่อไปนี้ ประการแรก สัญญาณรบกวนแบบครอสทอล์กเกิดจากค่าคาปาซิแตนซ์寄生และอินดักแตนซ์寄生 ประการที่สอง การดีคัปปลิงของริปเปิลแหล่งจ่ายไฟและแหล่งจ่ายไฟของชิปดิจิทัลที่ไม่ดีจะทำให้เกิดสัญญาณรบกวนบนแหล่งจ่ายไฟ ประการที่สาม อิมพีแดนซ์กราวด์และตำแหน่งกราวด์ของระบบทำให้เกิดสัญญาณรบกวน ปัญหาสัญญาณรบกวนควรถูกจัดการตามลำดับของแหล่งจ่ายไฟ สัญญาณ และกราวด์

แหล่งข้อมูลที่เป็นประโยชน์:

•บทนำที่ครอบคลุมที่สุดเกี่ยวกับเครื่องมืออัตโนมัติด้าน EMI และ EMC

•การรับประกันความสำเร็จตั้งแต่ครั้งแรกในการออกแบบ EMC ของแผงวงจรพิมพ์ (PCB)

•กฎการออกแบบการแบ่งส่วน PCB เพื่อปรับปรุง EMC

•การออกแบบแผงวงจรพิมพ์สำหรับวงจรความถี่วิทยุและความเข้ากันได้ทางแม่เหล็กไฟฟ้า

•สามข้อควรคำนึงด้านการออกแบบเพื่อให้มั่นใจใน EMC ของแผงวงจรพิมพ์ (PCB) แล็ปท็อป

•บริการผลิตแผงวงจรพิมพ์ (PCB) แบบครบทุกฟังก์ชันจาก PCBCart - ตัวเลือกเสริมที่เพิ่มมูลค่าหลากหลาย

•บริการประกอบแผงวงจรขั้นสูงจาก PCBCart - เริ่มต้นเพียง 1 ชิ้น