รูปแบบพื้นฐานที่สุดของการออกแบบเพื่อการผลิตเมื่อประยุกต์ใช้กับแผงวงจรพิมพ์ (PCB) คือการใช้กฎการออกแบบและการตรวจสอบกฎการออกแบบในซอฟต์แวร์ออกแบบ PCB การตรวจสอบกฎการออกแบบ (DRC) คือกระบวนการตรวจสอบแบบการออกแบบเพื่อดูว่าเป็นไปตามขีดความสามารถในการผลิตของผู้ผลิตแผงวงจรพิมพ์โดยทั่วไปแล้วผู้ออกแบบจะได้รับค่าความเผื่อสูงสุดที่ผู้ผลิตแผ่นวงจรพิมพ์ (PCB) รองรับจากผู้ผลิต จากนั้นจึงโหลดค่าความเผื่อเหล่านี้เข้าไปในโปรแกรมออกแบบของตน และรันการทดสอบกฎการออกแบบกับแบบร่างที่คาดหวังไว้ การตรวจสอบกฎการออกแบบมักถูกรวมอยู่ในซอฟต์แวร์ออกแบบ PCB และโดยทั่วไปไม่ได้ถือว่าเป็นบริการเสริม นอกจากนี้ยังมีซอฟต์แวร์วิเคราะห์การออกแบบเพื่อการผลิตขั้นสูงให้ใช้งาน เพื่อค้นหาข้อบกพร่องในการออกแบบที่ซับซ้อนและไม่ชัดเจนมากขึ้น โดยทั่วไปแล้วการตรวจสอบซอฟต์แวร์ DFMถูกนำเสนอโดยผู้ผลิตแผ่นวงจรพิมพ์ให้กับลูกค้าในฐานะบริการเสริม เหตุผลที่มีการแยกออกมาเช่นนี้เป็นเพราะต้นทุนเพิ่มเติมของซอฟต์แวร์ DFM ระดับสูงและการฝึกอบรมเพิ่มเติมที่จำเป็นต่อการใช้งาน

1. กระแสลมร้อนที่อ่อนแรง

การเชื่อมต่อแบบเทอร์มอลที่ขาดแคลน (Starved thermals) เกิดขึ้นเมื่อรอยต่อเทอร์มอลรีลีฟที่เชื่อมต่อกับแผด (pad) ไม่ได้เชื่อมต่ออย่างถูกต้องกับเพลนทองแดง (copper plane) ที่เกี่ยวข้อง บ่อยครั้งระยะห่างระหว่างเวีย (via) จะผ่านการตรวจสอบกฎการออกแบบพื้นฐาน แต่รอยต่อเทอร์มอลรีลีฟที่เชื่อมต่ออยู่จะถูกขัดจังหวะ และเวียที่ได้รับผลกระทบจะถูกแยกออกจากพื้นที่ทองแดงที่กำหนดให้โดยไม่เหมาะสม ปัญหานี้มักพบได้บ่อยเมื่อมีการวางเวียหลายตัวไว้ใกล้กัน

2. กับดักกรด

เมื่อรอยลายทองแดงสองเส้นเชื่อมต่อกันด้วยมุมแหลมมาก เป็นไปได้ว่าน้ำยากัดลายที่ใช้ในการกำจัดทองแดงออกจากแผ่นเปล่าอาจถูก “กัก” ไว้ที่จุดเชื่อมต่อเหล่านี้ กับดักนี้มักเรียกกันว่าแอซิดแทรป แอซิดแทรปอาจทำให้รอยลายทองแดงหลุดออกจากเน็ตที่กำหนดไว้ และทำให้รอยลายเหล่านี้กลายเป็นวงจรเปิด ปัญหาแอซิดแทรปได้ลดน้อยลงในช่วงไม่กี่ปีที่ผ่านมา เนื่องจากผู้ผลิตหันมาใช้น้ำยากัดลายที่ถูกกระตุ้นด้วยแสง ดังนั้น แม้ว่าการตรวจสอบให้แน่ใจว่ารอยลายทองแดงของคุณไม่ได้เชื่อมต่อกันด้วยมุมแหลมยังคงเป็นความคิดที่ดี แต่ปัญหานี้ก็ไม่ได้น่ากังวลเท่าในอดีต

3. ซิลเวอร์ส

หากส่วนเล็กมากของพื้นที่ทองแดงเชื่อมต่อกับส่วนที่ใหญ่กว่าของพื้นที่ทองแดงเดียวกันผ่านลายวงจรที่แคบ อาจทำให้ส่วนเหล่านั้นหลุดออกระหว่างกระบวนการผลิต ลอยไปยังส่วนอื่นของแผ่นวงจร และทำให้เกิดการลัดวงจรที่ไม่ตั้งใจได้ ปัญหาที่เกิดจากซิลเวอร์ได้รับการลดลงในช่วงไม่กี่ปีที่ผ่านมา เนื่องจากผู้ผลิตได้เปลี่ยนมาใช้สารละลายกัดกร่อนที่ถูกกระตุ้นด้วยแสง ดังนั้นแม้ว่าซิลเวอร์ยังคงเป็นสิ่งที่ควรหลีกเลี่ยงในการออกแบบ แต่ก็ไม่ได้เป็นปัญหาสำคัญเหมือนในอดีต

4. วงแหวนรอบรูไม่เพียงพอ

วิอาสร้างขึ้นโดยการเจาะผ่านแผดบนทั้งสองด้านของบอร์ดและชุบผนังของรูเหล่านี้เพื่อเชื่อมต่อสองด้านของบอร์ด หากขนาดแผดที่ระบุไว้ในแบบมีขนาดเล็กเกินไป วิอาอาจล้มเหลวได้เนื่องจากรูเจาะกินพื้นที่ของแผดมากเกินไป ขนาดวงแหวนแอนนูลาร์ขั้นต่ำมักเป็นส่วนหนึ่งของกระบวนการ DRC ประเด็นนี้ถูกกล่าวถึงที่นี่เนื่องจากการเกิดขึ้นไม่ใช่เรื่องแปลกของการเจาะพลาดในแผงต้นแบบ.

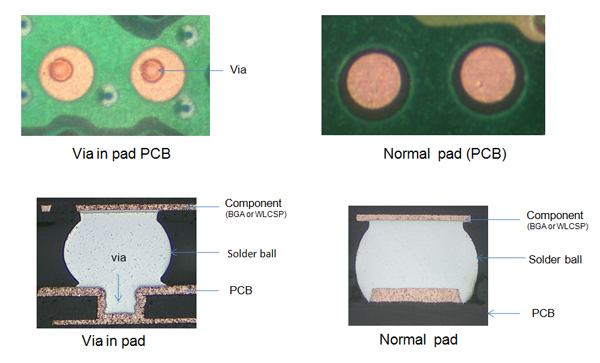

5. วีอาในแผ่น Pads

บางครั้งการออกแบบให้เวียถูกวางอยู่ภายในแผ่นแพดของแผ่นวงจรพิมพ์ (PCB) อาจเป็นเรื่องสะดวก อย่างไรก็ตาม เวียในแพดอาจทำให้เกิดปัญหาเมื่อถึงเวลาประกอบบอร์ด เวียจะดึงตะกั่วบัดกรีออกจากแพดและทำให้ชิ้นส่วนที่เชื่อมต่อกับแพดนั้นถูกติดตั้งไม่ถูกต้อง

ภาพด้านล่างแสดงให้เห็นความแตกต่างระหว่างผ่านในแผ่นรองPCB และ PCB ปกติ

6. ทองแดงอยู่ใกล้ขอบแผงวงจรมากเกินไป

โดยปกติแล้วจะถูกตรวจพบระหว่างการ检查กฎการออกแบบ การวางชั้นทองแดงใกล้กับขอบบอร์ดมากเกินไปอาจทำให้ชั้นเหล่านั้นลัดวงจรกันได้เมื่อบอร์ดถูกตัดให้ได้ขนาดระหว่างกระบวนการผลิต แม้ว่าข้อผิดพลาดลักษณะนี้ควรจะถูกตรวจพบโดยใช้ฟังก์ชัน DRC ที่มักมีให้ในซอฟต์แวร์ออกแบบ PCBผู้ผลิตแผงวงจรพิมพ์ (PCB) ที่ทำการตรวจสอบ DFM ก็จะสามารถตรวจพบปัญหานี้ได้เช่นกัน

7. ไม่มีหน้ากากบัดกรีระหว่างแผ่นแพด

ในอุปกรณ์ที่มีระยะห่างขาแน่นมากและมีระยะพิทช์ของขาเล็ก มักพบได้บ่อยว่าระหว่างขาจะไม่มีมาส์กบัดกรีเนื่องมาจากการตั้งค่ามาตรฐานในการออกแบบ การละเว้นมาส์กบัดกรีดังกล่าวอาจทำให้เกิดสะพานประสานได้ง่ายขึ้นเมื่อมีการติดตั้งชิ้นส่วนที่มีระยะพิทช์ขาละเอียดลงบนแผงวงจรพิมพ์ระหว่างกระบวนการประกอบ

เราได้ให้บริการบริการประกอบแผงวงจรพิมพ์ (PCB) แบบมืออาชีพตลอดหลายปีที่ผ่านมา เราสามารถหลีกเลี่ยงไม่ให้ขาดเลอะมาสก์บัดกรีระหว่างแผ่นรองได้ รูปภาพด้านล่างแสดงมาสก์บัดกรีความแม่นยำสูงของเราระหว่างแผ่นรอง QFN ระยะพิทช์ 0.4

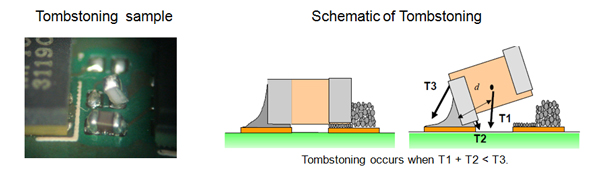

8. การกระโดดจากที่สูงลงน้ำ

เมื่อมีการบัดกรีชิ้นส่วนแบบติดตั้งผิวหน้าขนาดเล็กที่เป็นแบบพาสซีฟลงบนแผงวงจรพิมพ์ (PCB) ด้วยกระบวนการรีโฟลว์ มักเกิดกรณีที่ปลายด้านหนึ่งของชิ้นส่วนยกตัวขึ้นและเกิด “tombstone” การเกิด tombstoning สามารถส่งผลกระทบอย่างมากต่ออัตราผลผลิตของ PCB และทำให้ต้นทุนการผลิตเพิ่มสูงขึ้นอย่างรวดเร็ว สาเหตุของการเกิด tombstoning อาจมาจากรูปแบบแลนดิ้งที่ไม่ถูกต้องและการระบายความร้อนที่ไม่สมดุลไปยังแผ่นรองของอุปกรณ์ การใช้การตรวจสอบ DFM สามารถช่วยลดปัญหา tombstoning ได้อย่างมีประสิทธิภาพ

ภาพด้านล่างเป็นตัวอย่างการยกตัวของชิ้นส่วนและแผนผังวงจรของมัน

มีไฟล์ออกแบบ PCB อยู่ในมือแล้วหรือยัง? ให้ PCBCart ดูแลการผลิต PCB ของคุณ!