Heutzutage hat sich die Übertragungsrate von Hochleistungs-Computerverbindungsnetzwerken mit der Anwendung der Hochgeschwindigkeits-Serienübertragung von der ursprünglichen SDR (Single Data Rate, 2,5 Gb/s), DDR (Double Data Rate, 5 Gb/s) und QDR (Quad Data Rate, 10 Gb/s) zur FDR (Fourteen Data Rate, 14 Gb/s), der vierten Generation, entwickelt. Das Design von Leiterplatten (PCB)Leiterplatte) mit Verbindung und Schalttafel sowie Interface-Karten, die für die Bildung des Internets unerlässlich sind, ist in das FDR-Hochgeschwindigkeits- und Hochfrequenzfeld eingetreten. Da die Anstiegszeit des FDR-Signals drastisch auf die Größenordnung von 10 ps reduziert wurde, sind eine Reihe von Problemen bezüglich der Signalintegrität zu den Schlüsselfaktoren geworden, die die Möglichkeit der Funktionsimplementierung und den zuverlässigen Betrieb bestimmen, wie Dämpfung, Übersprechen, Reflexion, elektromagnetische Störungen usw. Basierend auf den Eigenschaften von FDR-Verbindungschips, einschließlich mehrerer Ports, mehrerer Kanäle, verschiedener Stromversorgungskategorien und hohem Energieverbrauch, ist es immer erforderlich, mehrere Verbindungschips auf einer einzigen Verbindungskarte zu integrieren, um die Durchsatzrate zu erhöhen. Auf einer Platine mit begrenztem Platz müssen einerseits einige Anforderungen erfüllt werden, darunterKomponentenlayoutund Wärmeableitung, Routing mit hoher Dichte, Langstreckenübertragung auf der Rückseite der Platine und Integrität aller Signalarten. Andererseits müssen einige Elemente berücksichtigt werden, darunter der PCB-Designzeitraum, die Einschränkungen der PCB-Fertigungstechnik und die Kostenkontrolle. Daher ist die Implementierung des Designs und die Simulationsverifizierung äußerst schwierig. Basierend auf dem PCB-Designbeispiel der FDR-Verbindung und der Switch-Platine stellt dieser Artikel einige Optimierungsmethoden in Bezug auf die Auswahl des Substratmaterials vor,Stack-up-Design, Routing-Regeln und Entstörungsdesign, um das Integritätsproblem aller Arten von Signalen im Prozess des FDR-Hochgeschwindigkeits-PCB-Designs zu lösen.

Dämpfungsattribut und Auswahl des Substratmaterials

Für FDR-Hochfrequenzsignale ist der Leitungsverlust das Problem, das die Signalintegrität betrifft. Wenn FDR-Signale vom Sendeterminal zum Empfangsterminal über Verbindungskanäle übertragen werden, kommt es aufgrund der Tatsache, dass die Hochfrequenzdämpfung wesentlich größer ist als die Niederfrequenzdämpfung, zu einer starken Verzerrung der Signalform am Empfangsterminal. Die Verzerrung lässt sich hauptsächlich in zwei Aspekte unterteilen: Die Spannungshöhe der Signale hat sich stark verringert, während die Anstiegsflanke des Signals stark verschlechtert wurde. Ersteres begrenzt die Übertragungsdistanz der Signale, während Letzteres zu einer Beeinträchtigung zwischen den Codes führt. Der Leitungsverlust A kann als Summe des Leiterverlusts betrachtet werdenABedingungund dielektrischer VerlustAdielwie in Formel (1) gezeigt:A=Adiel+ABedingung.

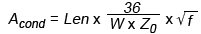

Leiterverlust bezieht sich auf den Verlust, der durch den Serienwiderstand auf dem Kupferleiter zwischen Signalpfad und Rückleitung verursacht wird. Bei hohen Frequenzen bewirkt der Skin-Effekt, dass der Strom an der Oberfläche der umgebenden Kupferleiter fließt. Mit dem Anstieg des äquivalenten Serienwiderstands der Kupferleiter steigt der Leiterverlust mit zunehmender Frequenz, wobei er proportional zur Quadratwurzel der Frequenz zunimmt, wie in Formel (2) dargestellt: .

.

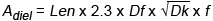

Dielektrischer Verlust bezieht sich auf den durch das Medium des Substratmaterials erzeugten Verlust, der hauptsächlich durch die Eigenschaften des Materials bestimmt wird und nicht mit der geometrischen Konstruktion einschließlich der Leiterbreite zusammenhängt. Er ist direkt proportional zur Frequenz, wie in Formel (3) dargestellt: .

.

Basierend auf Formel (2) kann die Erhöhung der Leiterbahnbreite den Leitungsverlust verringern. In der Praxis jedochLeiterplattendesignDie Breite von Leitern kann aufgrund der Begrenzung des Abstands zwischen Pins, der Platine, der Anzahl der Signallagen und des Widerstands niemals unbegrenzt groß sein. Die üblicherweise im FDR-Design angewandte Leiterbreite/-abstand/-breite beträgt in der Regel 7mil/7mil/7mil oder 8mil/10mil/8mil. Bei gleicher Leiterbreite ist der Leiterverlust proportional zur Leiterlänge und steht in keinem Zusammenhang mit dem Material. Daher muss zur Verringerung des gesamten Übertragungsverlusts nur der dielektrische Verlust berücksichtigt werden. Nach Formel (3) ist der dielektrische Verlust proportional zum Verlustfaktor, und die Anwendung kleiner Verlustfaktoren kann zur Verringerung des dielektrischen Verlusts beitragen, was wiederum den Gesamtübertragungsverlust reduziert.

Tabelle 1 listet die Attributparameter von drei gewöhnlichen Hochgeschwindigkeits-Leiterplattenmaterialien sowie die nach Formel (1), (2) und (3) berechneten Verlustwerte bei einer Übertragungsrate von 14 Gb/s, einer Leiterbahnbreite von 8 mil und einem Widerstand von 50 Ω auf.

|

Plattenmaterialparameter

|

FR4

|

Nelco4000-13SI

|

Megtron6

|

| Df@10GHz |

0,02 |

0,008 |

0,004 |

| Dk@10GHz |

4,10 |

3.200 |

3.600 |

| ABedingung@7GHz/in |

0,24 |

0,240 |

0,240 |

| Adiel@7GHz/in |

0,65 |

0,230 |

0,120 |

| A@7GHz/in |

0,89 |

0,470 |

0,360 |

| A@7GHz/30in |

27,00 |

14.000 |

11.000 |

| Relative Kosten |

1,00 |

3.500 |

8.000 |

Es kann festgestellt werden, dass bei einer Übertragungsrate von 14 Gb/s und einer Übertragungslänge von 30 Zoll der gesamte Übertragungsverlust von Nelco4000-13SI etwa 14 dB beträgt, während die Spannungsschwächung, die ein typischer FDR-Chip verkraften kann, im Bereich von 20 dB bis 25 dB liegt. Daher kann dieses Leiterplattenmaterial im Design von FDR-Verbindungsschaltkarten mit einer Übertragungsdistanz von weniger als 30 Zoll eingesetzt werden. Der gesamte Übertragungsverlust von FR4 beträgt jedoch etwa 27 dB, sodass FR4 für FDR-Designs mit großer Übertragungsdistanz nicht geeignet ist. Für FDR-Verbindungsschnittstellenkarten mit kurzer Übertragungsdistanz kann jedoch FR4 gewählt werden, um die Kosten zu senken. Megtron6 hingegen weist die geringste Gesamtübertragungsdämpfung auf, ist jedoch am teuersten, und sein Einsatz in FDR führt zu einer Erhöhung der Systemarchitekturkosten. Zusammenfassend gilt fürHochfrequenz-Leiterplatte, Das Plattenmaterial ist die Grundlage, und die Auswahl des Plattenmaterials bestimmt die Übertragungslänge der Signale.

Layout- und Stapeldesign

Für das PCB-Design müssen zunächst die Struktur und der Aufbau der Leiterplatte berücksichtigt werden. In der Regel sind das Muster und die Form der Leiterplatte bereits festgelegt, und die Bestimmung der Lagenanzahl hängt von der Signalfrequenz und der Pin-Dichte der Leiterplatte ab.Leiterplattenherstellungskosten, Fertigungszeitraum und Zuverlässigkeitsanforderungen. FDR-Verbindungsschaltplatten weisen eine hohe Frequenz und Dichte auf, und der Einsatz von Mehrlagenplatinen ist ein notwendiger Schritt zur Reduzierung von Störungen. Darüber hinaus ist die Festlegung der Lagenanzahl entscheidend.

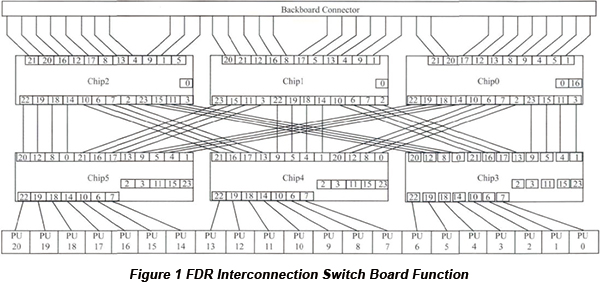

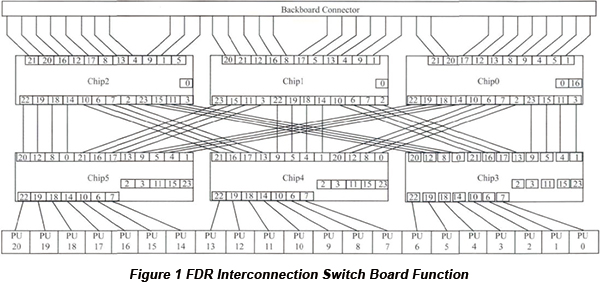

Auf dem FDR-Verbindungschip gibt es 24 Ports, und jeder Port verfügt im Betriebsmode der Kopplung über 8 Tx-Kanäle und 8 Rx-Kanäle. Die FDR-Verbindungsplatine verwendet 6 Verbindungschips und 3 Downlink-Chips, und 32 Ports werden über den Backboard-Steckverbinder angeschlossen. 3 Uplink-Chips greifen über QSFP (Quad Small Form-factor Pluggable) Lichtwellenleiter auf 21 Ports zu. Uplink-Chip und Downlink-Chip sind über 4 Ports miteinander verbunden, wie in Abbildung 1 dargestellt.

FDR bietet das Paket vonBGA (Ball Grid Array)Mit einer Fläche von 50 mm x 50 mm, 1157 Pins und einem Abstand von 1,0 mm sowie P/N-Pins an den Ports von Tx und Rx sind die Pins gemäß drei konzentrischen Kreisen verteilt. Theoretisch können drei Signallagen verwendet werden, um alle Pins an allen Ports aus dem BGA herauszuführen. Unter Berücksichtigung der folgenden zwei Elemente können zwei Signallagen verwendet werden, um eine Gruppe von Pins der konzentrischen Kreise zu erreichen.

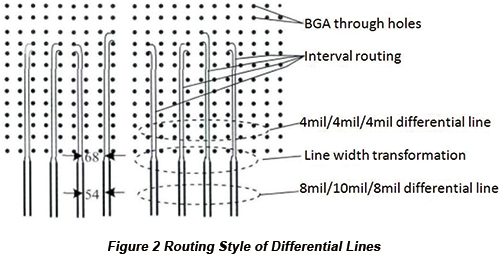

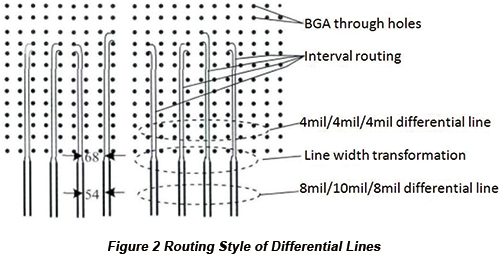

a. Aufgrund der Platzbeschränkung beträgt die Leiterbahnbreite/-abstand/-breite der differentiellen Leitungen 4mil/4mil/4mil und wird beim Austritt aus dem BGA auf 8mil/10mil/8mil erweitert. Der Abstand zwischen den differentiellen Leitungspaaren sollte mindestens 50mil betragen. Daher muss ein differentielles Leitungspaar eine Breite von 2mm einnehmen und 48 Signalpaare verlaufen entlang der Kante mit der höchsten Dichte. Daher ist es schwierig, diese Methode umzusetzen.

b. Der Abstand zwischen den BGA-Pins beträgt 1 mm. Wenn eine Signallage verwendet wird, um auf eine Gruppe konzentrischer Kreissignale zuzugreifen, beträgt der Abstand zwischen den differentiellen Leitungspaaren unter dem BGA nur 14 mil, was weit von den erforderlichen 50 mil entfernt ist. Außerdem beträgt die maximale parallele Leitungsführungslänge nur 20 mm, was zu etwas Übersprechen führen wird.

Um die oben genannten negativen Faktoren zu vermeiden, werden zwei Signallagen verwendet, um auf eine Gruppe konzentrischer Kreissignale zuzugreifen, und das differentielle Signal jeder Signallage muss gemäß einem Abstand von 50 mil aus dem BGA herausgeführt werden. Daher sind für FDR-Verbindungsplatinen mindestens 6 Lagen erforderlich, um alle differentiellen Signale aus dem BGA herauszuführen. Unter Berücksichtigung der Konnektivität und der Routing-Menge der Platine sowie ausreichend Platz für Austausch-Kopplungskondensatoren werden 8 interne Signallagen und ein 22-Lagen-Stack verwendet.

Übersprechungsanalyse und Reduktionsmaßnahmen

Übersprechen ist der erste Aspekt, der bei der Hochgeschwindigkeits- und Hochdichteschaltungsentwicklung berücksichtigt werden muss. Wenn sich Spannung und Strom in der Störleitung ändern, kommt es durch gegenseitige Kapazität und gegenseitige Induktivität zwischen Störleitung und Opferleitung zu elektromagnetischer Kopplung. Das Übersprechen, das entlang der Opferleitung in Richtung Sendeterminal fließt, wird als Nah-Ende-Übersprechen bezeichnet, während das Übersprechen, das entlang der Opferleitung in Richtung Empfangsterminal fließt, als Fern-Ende-Übersprechen bezeichnet wird. Im Allgemeinen sollte die gesamte Störspannung auf der Opferleitung auf weniger als 5 % der Signalspannung begrenzt werden. Am besten wird das Übersprechen einer einzelnen Störleitung auf weniger als 1 % begrenzt, wobei andere Störquellen und Störleitungen auf beiden Seiten der Opferleitung berücksichtigt werden.

Die wichtigsten Punkte zur Reduzierung von Übersprechen umfassen:

a. Der Abstand zwischen der Störleitung und der Opferleitung sollte vergrößert und die parallele Leitungsführung verkürzt werden.

b. Integrierte Masse wird als Rückweg für Signale verwendet. Nach empirischer Regel beträgt bei einer 50Ω-Leiterbahn (Stripline) das Near-End-Crosstalk etwa 0,5 %, wenn der Abstand das Dreifache der Leiterbahnbreite beträgt. Bei einer 50Ω-Mikrostreifenleitung (Microstrip Line) beträgt das Near-End-Crosstalk etwa 1 %, wenn der Abstand das Dreifache der Leiterbahnbreite beträgt. Das Far-End-Crosstalk auf Striplines oder vollständig eingebetteten Mikrostreifenleitungen ist nahezu null, und die Far-End-Crosstalk-Polarität von Mikrostreifen-Übertragungsleitungen ist negativ, wobei die Größe relativ groß ist, da der Einfluss der induktiven Kopplung größer ist als der der kapazitiven Kopplung.

• Intervall-Routing

In diesem Design beträgt die differentielle Impedanz der Hochgeschwindigkeits-Differenzleitung 100Ω. Basierend auf dem Si9000-Feldlöser wurde die Leiterbahnbreite/-abstand/-leiterbahnbreite auf 8mil/10mil/8mil berechnet. Je breiter die Leiterbahn ist, desto geringer ist die Dämpfung, und der Abstand von 10mil dient dazu, die differentielle Impedanz von 100Ω aufrechtzuerhalten. Dieser Typ von Differenzleitung wird außerhalb des BGA-Chipbereichs angewendet. Um Übersprechen zu verringern, beträgt der Abstand zwischen zwei Paaren von Differenzleitungen mindestens 80mil. Der Abstand zwischen den Pins des Verbindungschips in diesem Artikel beträgt 1mm, und die Begrenzung der Durchgangslochgröße des BGA führt dazu, dass die Leiterbahnbreite/-abstand/-leiterbahnbreite der Differenzleitung im BGA-Chipbereich 4mil/4mil/4mil beträgt. Obwohl die differentielle Impedanz dieses Typs von Differenzleitung ebenfalls 100Ω beträgt, ist der Leitungsverlust groß, sodass die Differenzleitung von 4mil/4mil/4mil so schnell wie möglich in 8mil/10mil/8mil umgewandelt werden muss, sobald sie in den BGA-Chipbereich eintritt. Um Übersprechen zu reduzieren, wird im BGA-Chipbereich für die Differenzleitung von 4mil/4mil/4mil die Methode des Intervall-Routings angewendet, um ebenfalls sicherzustellen, dass der Abstand zwischen zwei Paaren von Differenzleitungen mehr als 50mil beträgt, wie in Abbildung 2 gezeigt.

• Differenzielle Bohrungen

In diesem Design werden spezielle differentielle Bohrungen vorgesehen, um die Anwendung der Austausch-Kopplungskapazität auf der Verbindungsschicht zu ermöglichen. Neben den differentiellen Bohrungen müssen Massebohrungen platziert werden, um einen Rückflusskanal für den Rückweg bereitzustellen. Das Design mit vier Massebohrungen bietet die beste Wirkung, aber auch zwei Massebohrungen können verwendet werden, wenn der Platz auf der Leiterplatte begrenzt ist. Darüber hinaus sollten Maßnahmen wie Rückbohren und das Entfernen interner Pads bei differentiellen Bohrungen ergriffen werden, um die Impedanzänderung an den differentiellen Bohrungen zu verringern und so Übersprechen und Reflexionen zu reduzieren.

• Verhindern, dass Tx und Rx in derselben Schicht geführt werden

Um Übersprechen zu reduzieren, sollte die Tx-Differenzleitung in einer anderen Lage als die Rx-Differenzleitung geführt werden. Hierbei bezieht sich Tx auf das Quellterminal der Differenzleitung, während Rx das Empfangsterminal der Differenzleitung bezeichnet. Falls beide in derselben Lage geführt werden müssen, sollte der Abstand zwischen ihnen mehr als 5 mm betragen, um die Sicherheit zu gewährleisten.

• 20H-Regel

In der Leiterplattenschaltung mit hoher Frequenz und hoher Geschwindigkeit wird HF-Energie durch die Stromversorgungsschicht und die Massefläche der Leiterplatte gekoppelt, und zwischen der Stromversorgungsschicht und der Massefläche entsteht ein Rand-Magnetflussleck. Die Funkfrequenzenergie kann in den freien Raum abgestrahlt werden. Die 20H-Regel besagt, dass, wenn auf der Platine Hochgeschwindigkeitsströme vorhanden sind, damit verbundene elektromagnetische Felder existieren. Im Design dieses Artikels sollte der Abstand zwischen allen Leiterbahnen und dem Platinenrand mindestens das 20-fache der Leiterbahnbreite betragen und der Abstand zwischen Hochgeschwindigkeits-Differenzbohrungen und den Trennlinien der Stromversorgungsebene mindestens 5 mm betragen.

• Routing auf der Oberflächenschicht

Beim Design von Hochfrequenz-Leiterplatten ist aufgrund des relativ großen Fernübersprechens zwischen Mikrostreifenleitungen und Streifenleitungen die Führung von Hochgeschwindigkeits-Differenzleitungen auf der Oberflächenschicht untersagt. Im Design dieses Artikels sind aufgrund der Beschränkungen des Fertigungsverfahrens maximal 8 interne Leitungsebenen erforderlich. Darüber hinaus macht die Einschränkung der Anschlussanordnung des Verbindungschips es unmöglich, die Verbindungen der differentiellen Verbindungsleitungen zwischen den 6 Chips innerhalb der Verbindungsplatine ausschließlich über interne Ebenen zu realisieren.

.

. .

.