Impedanzkontrolltechnologien sind in der Hochgeschwindigkeits-Digitalschaltungsentwicklung von großer Bedeutung, da wirksame Methoden eingesetzt werden müssen, um die hervorragende Leistung von Hochgeschwindigkeits-PCBs sicherzustellen.

Impedanzberechnung und Impedanzkontrolle von Hochgeschwindigkeits-Leiterbahn-Übertragungsleitungen auf Leiterplatten

• Äquivalentes Modell für Übertragungsleitungen

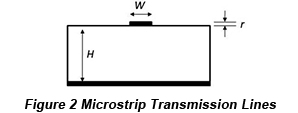

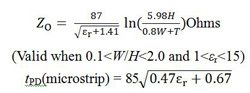

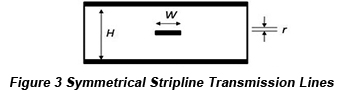

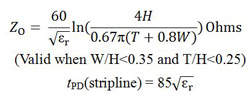

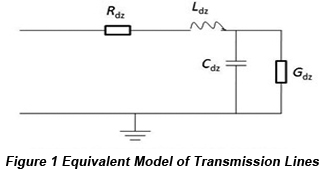

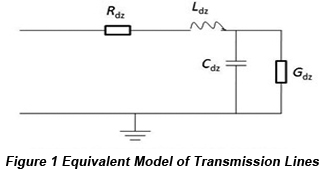

Abbildung 1 zeigt die äquivalente Wirkung von Übertragungsleitungen auf Leiterplatten, die eine Struktur mit in Reihe geschalteten und mehreren Kondensatoren, Widerständen und Induktivitäten (RLGC-Modell) darstellt.

Der typische Wert des Tandemwiderstands liegt im Bereich von 0,25 bis 0,55 Ohm/Fuß, und der Widerstandswert mehrerer Widerstände bleibt in der Regel recht hoch. Mit der parasitären Widerstands-, Kapazitäts- und Induktivitätseinwirkung in Leiterbahnen auf Leiterplatten wird die Gesamtimpedanz auf Leiterbahnen als charakteristische Impedanz (Z) bezeichnet.0). Der Wert des Wellenwiderstands ist relativ klein, wenn der Leitungsdurchmesser groß ist, die Leitung nahe an Stromversorgung/Masse liegt oder die Dielektrizitätskonstante hoch ist. Abbildung 3 zeigt das Ersatzmodell der Übertragungsleitung mit einer Länge von dz, auf dessen Grundlage der Wellenwiderstand der Übertragungsleitung gemäß der Formel hergeleitet werden kann: . In dieser Formel,Lbezieht sich auf die Induktivität je Längeneinheit der Übertragungsleitung, währendCbezieht sich auf die Kapazität je Längeneinheit der Übertragungsleitung.

. In dieser Formel,Lbezieht sich auf die Induktivität je Längeneinheit der Übertragungsleitung, währendCbezieht sich auf die Kapazität je Längeneinheit der Übertragungsleitung.

• Impedanzkontroll-Layoutregeln für Übertragungsleitungen

Basierend auf der obigen Analyse steht die Einheitsverzögerung von Impedanz und Signal nicht in Beziehung zur Frequenz der Signale, sondern hängt mit der Leiterplattenstruktur, der relativen Dielektrizitätskonstante des Leiterplattenmaterials und den physikalischen Eigenschaften der Leiterbahnen zusammen. Diese Schlussfolgerung ist für das Verständnis äußerst wichtig.Hochgeschwindigkeits‑Leiterplatteund für das High-Speed-PCB-Design. Darüber hinaus ist die Übertragungsgeschwindigkeit der Signalleitung in der Außenlage deutlich höher als in der Innenlage, sodass diese Faktoren bei der Anordnung des Layouts der Schlüssel-Leitungen berücksichtigt werden müssen.

Die Impedanzsteuerung ist die wesentliche Voraussetzung für die Umsetzung der Signalübertragung. Allerdings hängt die Impedanz gemäß der Leiterplattenstruktur und der Impedanzberechnungsformel für Übertragungsleitungen nur ab vonLeiterplattenmaterialundPCB-Lagenaufbauwobei die Leiterbahnbreite und die Routing-Eigenschaften für dieselbe Leiterbahn unverändert bleiben. Daher ändert sich der Wellenwiderstand einer Leiterbahn auf verschiedenen PCB-Lagen nicht, was im Hochgeschwindigkeits-Schaltungsdesign nicht zulässig ist.

Für diesen Artikel wird eine Hochgeschwindigkeits‑Leiterplatte mit hoher Dichte entworfen, und die meisten Signale auf der Platine haben Impedanzanforderungen. Zum Beispiel sollte die CPCI‑Signalleitung eine Impedanz von 65 Ohm, das differentielle Signal von 100 Ohm und alle anderen Signale jeweils von 50 Ohm aufweisen. EntsprechendLeiterplattenroutingIm Raum muss eine mindestens zehnlagige Leiterführung verwendet werden, und es wird ein 16-lagiger Leiterplatten-Designplan festgelegt.

Da die Gesamtdicke der Leiterplatte 2 mm nicht überschreiten darf, gibt es einige Schwierigkeiten beim Stapeln, wobei einige Probleme berücksichtigt werden müssen:

1).Jede Signallage verfügt über benachbarte Bildebenen, die die Impedanz und Signalqualität schützen.

2).Jede Versorgungsebene verfügt über eine vollständige, angrenzende Masseebene, sodass die Leistungsfähigkeit der Stromversorgung gut sichergestellt ist.

3).Das Stapeln der Leiterplatten erfordert Ausgewogenheit, wobei eine Verwerfung der Leiterplatten vermieden werden muss.

Die Dielektrizitätskonstante des Mediums wird auf 4,3 festgelegt. Basierend auf dem obigen Lagenaufbau sollten die Leiterbahnbreite und der Abstand zwischen den Leiterbahnen entsprechend dem Berechnungsergebnis festgelegt werden, um die Anforderungen an die Signalimpendanz zu gewährleisten. Die Leiterbahnbreite ergibt sich wie folgt:

1).Die Breite der Signalleitung auf der Oberflächenschicht beträgt 5 mil und ihre Impedanz 58,7 Ohm.

2).Die Breite der CPCI-Signalleitung auf der Oberflächenschicht beträgt 4,5 mil bei einem Wellenwiderstand von 61,7 Ohm.

3).Die Breite der Signalleitung in der Innenlage beträgt 4,5 mil bei einem Wellenwiderstand von 50,2 Ohm.

4).Die Leiterbahnbreite im BGA-Bereich in der Innenlage und der Außenlage beträgt 4 mil, mit einer Impedanz von 64,6 Ohm in der Außenlage und 52,7 Ohm in der Innenlage.

5).Die Breite der Mikrostreifen-Differenzleitung in der Innenlage beträgt 5 mil bei einem Leitungsabstand von 6 mil und einer Impedanz von 100,54 Ohm.

6).Die Breite der Stripline-Differenzleitung in der Innenlage beträgt 4,5 mil bei einem Leitungsabstand von 10 mil und einer Impedanz von 96,6 Ohm.

Der Zeilenabstand ist wie folgt festgelegt:

1).Der Abstand zwischen Signalleitungen (5 mil) auf der Oberflächenschicht beträgt 5,0 mil.

2).Der Abstand zwischen den CPCI-Signalleitungen (4,5 mil) auf der Oberflächenschicht beträgt 9,0 mil.

3).Der Abstand zwischen Signalleitungen (4,5 mil) in der Innenlage beträgt 7,0 mil.

4).Der Abstand zwischen den Leiterbahnen auf der Außenlage und der Innenlage beträgt 4,0 mil.

5).Der Abstand zwischen differentiellen Signalleitungen in der Innenlage sowie zwischen ihnen und anderen Signalleitungen sollte mindestens 25 mil betragen.

6).Der Abstand zwischen differentiellen Signalleitungen auf der Oberflächenschicht sowie zwischen ihnen und anderen Signalleitungen sollte mindestens 20 mil betragen.

NachPCB-DruckDer Wellenwiderstand der Testplatine wird mit dem POLAR-Cits500-Wellenwiderstandstester gemessen, die Ergebnisse sind in der folgenden Tabelle aufgeführt. Die Daten zeigen, dass der Wellenwiderstand im Prozess des Hochgeschwindigkeits‑PCB‑Designs und der -Fertigung im Bereich von 50 Ohmۯ%, 60 Ohmۯ% und 100 Ohmۯ% kontrolliert werden muss.

|

Voreingestellter Widerstand (Ohm)

|

Praktische Impedanz (Ohm)

|

| 50 |

47,52–52,33 |

| sechzig |

57,65–61,35 |

| 100 |

93,65–106,35 |

LVDS und seine Impedanzkontrolle auf Leiterplatten

• LVDS

LVDS ist eine Art von hochgeschwindigem seriellen Signalübertragungspegel mit den Vorteilen hoher Übertragungsgeschwindigkeit, geringem Stromverbrauch, starker Störfestigkeit, großer Übertragungsentfernung und einfacher Anpassbarkeit. Die Anwendungsbereiche von LVDS umfassen Computer, Kommunikation und Konsumgüter.

• Impedanzdesign von LVDS

LVDS weist eine Spannungsschwankung von nur 350 mV auf, bei einer maximalen Übertragungsdistanz von über 10 Metern. Um sicherzustellen, dass Signale während der Übertragung in Leitungen nicht durch reflektierte Signale beeinflusst werden, muss die Impedanz der Übertragungsleitungen kontrolliert werden, mit einer Leitungsimpedanz von 50 Ohm für Einzelleitungen und 100 Ohm für differentielle Leitungen. In der praktischen Anwendung kann die Impedanz durch eine sinnvolle Festlegung der Lagenstärken und Dielektrikumsparameter, durch Anpassung der Leiterbahnbreite und des Abstands zwischen den Leiterbahnen sowie durch Berechnung der Impedanz von Einzelleitungen und differentiellen Leitungen mit Hilfe einiger Hochgeschwindigkeits-Simulations- und Analysetools kontrolliert werden.

Allerdings ist es in den meisten Fällen relativ schwierig, die Anforderungen an die Einzelleitungsimpedanz und die differentielle Impedanz zu erfüllen. Einerseits wird der Einstellbereich der Leiterbahnbreite W und des Abstands zwischen den Leiterbahnen S durch den verfügbaren physikalischen Designraum begrenzt. Zum Beispiel werden das Routing und die Leiterbahnbreite in den Randsteckverbindern mit BGA oder DIP durch die Padgröße und die Abstände beeinflusst. Andererseits wirken sich Änderungen von W und S auf das Ergebnis der Einzelleitungs- und differentiellen Impedanz aus. Bis jetzt ist es einfach und bequem, die Beziehung zwischen voreingestellter Leiterbahnbreite und Leiterbahnabstand zu ermitteln.

• LVDS-Routing-Regeln

Im Allgemeinen wird die Differenzsignalführung gemäß den Impedanz-Designregeln implementiert, was die Qualität von LVDS sicherstellen kann. In der praktischen Leiterbahnführung sollte LVDS den folgenden Regeln entsprechen:

1).Differenzpaare sollten so kurz wie möglich sein, die Leitungen sollten gerade verlaufen und die Anzahl der Durchkontaktierungen sollte verringert werden. Der Abstand zwischen den Signalleitungen in Differenzpaaren sollte gleich sein. All diese Regeln tragen dazu bei, lange Leitungsführungen und zahlreiche Richtungsänderungen zu vermeiden. Was Richtungsänderungen betrifft, sollten 45‑Grad‑Abzweigungen anstelle von 90‑Grad‑Abzweigungen verwendet werden.

2).Der Abstand zwischen differentiellen Paaren sollte mehr als das Zehnfache betragen, um das Übersprechen zwischen den Leitungen zu verringern. Bei Bedarf können zur Isolation Masse-Durchkontaktierungen zwischen differentiellen Paaren platziert werden.

3).LVDS kann nicht über verschiedene Ebenen aufgeteilt werden. Obwohl zwei differentielle Signale gegenseitige Rückstrompfade sind, darf der Rückstrompfad des Signals aufgrund einer Aufteilung über verschiedene Ebenen nicht unterbrochen werden. Dennoch können Übertragungsleitungen aufgrund fehlender Referenzebenen möglicherweise zu Impedanzdiskontinuitäten führen.

4).Vermeiden Sie differentielle Signale zwischen den Lagen. Während der Leiterplattenherstellung ist die Stapelausrichtungsgenauigkeit zwischen den Lagen deutlich geringer als die Ätzgenauigkeit innerhalb derselben Lage, zuzüglich der Verluste im Dielektrikum während des Stapelns, was insgesamt zu einer Veränderung der differentiellen Impedanz zwischen differentiellen Paaren führt.

5).In der Impedanzgestaltung sollte eine Kopplungsmethode verwendet werden.

6).Eine geeignete PCB-Stacking-Struktur sollte festgelegt werden, um die Isolation zwischen Signalen unterschiedlicher Spannungspegel und LVDS sicherzustellen. Wenn möglich, können Signale wie High-Speed-TTL/CMOS auf verschiedenen Lagen geführt und durch Masse- und Versorgungslagen von der LVDS-Routingführung isoliert werden.

7).Differentielle Signalleitungs-Paare sollten mit der Länge der Leiterbahnführung kompatibel sein.

Die Impedanzsteuerung wird bei der Entwicklung von Hochgeschwindigkeits-Digitalschaltungen sehr effektiv eingesetzt, um eine gute Leistung von Hochgeschwindigkeits-PCBs sicherzustellen. Durch sorgfältige Kontrolle der Leiterbahnbreite, des Lagenaufbaus und der Dielektrizitätskonstanten können Entwickler die korrekten Impedanzwerte erreichen, die für eine maximale Minimierung von Signalreflexionen und die Wahrung der Signalintegrität erforderlich sind. Korrekte Führung und Planung, insbesondere für LVDS-Signale, gewährleisten zudem eine einwandfreie Signalübertragung, Zuverlässigkeit und eine störungsfreie Ausbreitung.

PCBCart ist auf die Entwicklung und Herstellung leistungsstarker High-Speed-Leiterplatten für anspruchsvolle Anwendungen spezialisiert. Unsere hochmoderne Technologie und unser fortschrittliches Fachwissen gewährleisten präzise Impedanzkontrolle, hochwertige Leiterplatten und eine effektive Signalübertragung. Mit unserem hochmodernen Produktionsprozess und unserer Leidenschaft für Spitzenleistungen ist PCBCart Ihr erstklassiger Partner für komplexe Leiterplattenprojekte. Fordern Sie noch heute ein Angebot von PCBCart an und erleben Sie unvergleichlichen Service bei High-Speed-PCB-Lösungen, die darauf ausgelegt sind, Ihre Innovation und Ihren Erfolg voranzutreiben.

Starten Sie Ihr Angebot für Hochgeschwindigkeits-Leiterplatten

. In dieser Formel,

. In dieser Formel,