En la actualidad, la velocidad de transmisión de la red de interconexión de computadoras de alto rendimiento con la aplicación de transmisión serie de alta velocidad ha evolucionado hasta FDR (Fourteen Data Rate, 14 Gb/s), la cuarta generación desde la SDR (Single Data Rate, 2,5 Gb/s) inicial, DDR (Double Data Rate, 5 Gb/s) y QDR (Quad Data Rate, 10 Gb/s). El diseño de PCB (Placa de circuito impreso) con la interconexión, el tablero de conmutación y las tarjetas de interfaz que son esenciales para la formación de Internet, ha entrado en el campo FDR de alta velocidad y alta frecuencia. Dado que el tiempo de subida de la señal FDR se ha reducido drásticamente al orden de magnitud de 10 ps, una serie de problemas relacionados con la integridad de la señal se ha convertido en la característica clave para determinar la posibilidad de implementación de la funcionalidad y el funcionamiento fiable, tales como atenuación, diafonía, reflexión, interferencia electromagnética, etc. Basado en las características de los chips de interconexión FDR, que incluyen múltiples puertos, múltiples canales, múltiples categorías de potencia y alto consumo de energía, siempre se requiere integrar múltiples chips de interconexión en una sola placa de interconexión con el fin de aumentar la tasa de rendimiento. En una placa con espacio limitado, por un lado, deben cumplirse algunos requisitos, incluyendodiseño de componentesy disipación de calor, enrutamiento con alta densidad, transmisión a larga distancia a través de la parte posterior de la placa e integridad de todo tipo de señales. Por otro lado, deben tenerse en cuenta algunos elementos, incluidos el período de diseño de PCB, las limitaciones de la técnica de fabricación de PCB y el control de costos. Por lo tanto, es extremadamente difícil la implementación del diseño y la verificación mediante simulación. Basado en el ejemplo de diseño de PCB de interconexión FDR y placa de conmutación, este artículo presenta algunos métodos de optimización en términos de selección de material del sustrato,diseño de apilamiento, reglas de enrutamiento y diseño antiinterferencias para resolver el problema de integridad de todo tipo de señales en el proceso de diseño de PCB de alta velocidad FDR.

Selección de atributos de atenuación y material de sustrato

Para las señales de alta frecuencia FDR, la pérdida en la línea de transmisión es el problema relacionado con la integridad de la señal. Cuando las señales FDR se transmiten desde el terminal emisor al terminal receptor a lo largo de los canales de interconexión, debido a que la atenuación de alta frecuencia es mucho mayor que la atenuación de baja frecuencia, se produce una grave deformación en la forma de onda de la señal que llega al terminal receptor. La deformación se clasifica principalmente en dos aspectos: el margen de tensión de las señales ha disminuido considerablemente, mientras que se ha producido una fuerte degradación en el flanco de subida de la señal. El primero limita la distancia de transmisión de las señales, mientras que el segundo provoca interferencia entre códigos. La pérdida de la línea de transmisión A puede considerarse como la suma de la pérdida del conductorAcondy pérdida dieléctricaAdielcomo se muestra en la Fórmula (1):A=Adiel+Acond.

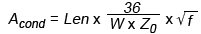

La pérdida del conductor se refiere a la pérdida causada por la resistencia en serie en el conductor de cobre entre la trayectoria de la señal y la trayectoria de retorno. En situaciones de alta frecuencia, el efecto pelicular hace que la corriente fluya en la superficie de los conductores de cobre circundantes. Con el aumento de la resistencia serie equivalente de los conductores de cobre, la pérdida del conductor aumentará con el incremento de la frecuencia, siendo directamente proporcional a la raíz cuadrada de la frecuencia, lo cual se ilustra en la Fórmula (2): .

.

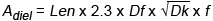

La pérdida dieléctrica se refiere a la pérdida generada por el medio del material del sustrato, determinada principalmente por las propiedades del material y no relacionada con la estructura geométrica, incluida la anchura del conductor, siendo directamente proporcional a la frecuencia, lo cual se muestra en la Fórmula (3): .

.

Según la Fórmula (2), el aumento del ancho de línea es capaz de reducir la pérdida del conductor. Sin embargo, en la prácticaDiseño de PCBel ancho de los conductores nunca puede ser indefinidamente grande como resultado de la limitación del espaciado entre pines, la placa, el número de capas de señal y la impedancia. El ancho/espaciado/ancho de conductor comúnmente aplicado en el diseño FDR suele ser 7mil/7mil/7mil o 8mil/10mil/8mil. Cuando el ancho del conductor es el mismo, la pérdida del conductor es directamente proporcional a la longitud del conductor, sin ninguna relación con el material. Por lo tanto, para reducir la pérdida total de transmisión, solo es necesario tener en cuenta la pérdida dieléctrica. Con base en la Fórmula (3), la pérdida dieléctrica es proporcional al factor de disipación y la aplicación de factores de disipación pequeños puede ayudar a la reducción de la pérdida dieléctrica, lo que conduce a la reducción de la pérdida total de transmisión.

La Tabla 1 enumera los parámetros de los atributos de tres materiales ordinarios de placas de alta velocidad y los valores de pérdida calculados según las Fórmulas (1), (2) y (3) cuando la velocidad de transmisión es de 14 Gb/s, el ancho del conductor es de 8 mil y la impedancia es de 50 Ω.

|

Parámetros del material de la placa

|

FR4

|

Nelco4000-13SI

|

Megtron6

|

| Df@10GHz |

0,02 |

0,008 |

0,004 |

| Dk@10GHz |

4.10 |

3.200 |

3.600 |

| Acond@7GHz/in |

0,24 |

0,240 |

0,240 |

| Adiel@7GHz/en |

0,65 |

0,230 |

0,120 |

| A@7GHz/pulg |

0,89 |

0,470 |

0,360 |

| A@7GHz/30in |

27,00 |

14.000 |

11.000 |

| Costo relativo |

1,00 |

3.500 |

8.000 |

Se puede indicar que, con una tasa de transmisión de 14 Gb/s y una longitud de transmisión de 30 pulgadas, la pérdida de transmisión total de Nelco4000-13SI es de aproximadamente 14 dB, mientras que la atenuación del nivel de tensión que un chip FDR típico puede soportar está en el rango de 20 dB a 25 dB. Por lo tanto, este tipo de material de placa puede aplicarse en el diseño de placas de conmutación de interconexión FDR con una distancia de transmisión inferior a 30 pulgadas. Sin embargo, la atenuación total de transmisión de FR4 es de aproximadamente 27 dB y FR4 no puede aplicarse al diseño FDR de larga distancia, pero en las tarjetas de interfaz de interconexión FDR con distancias de transmisión cortas se permite seleccionar FR4 para reducir el costo. En cuanto a Megtron6, cuya atenuación total de transmisión es la más pequeña, presenta el costo más alto y su aplicación en FDR conduce al aumento de los costos de la arquitectura del sistema. En conclusión, paraPCB de alta frecuencia, el material de la placa es la base y la selección del material de la placa determina la longitud de transmisión de las señales.

Diseño de distribución y pila

Para el diseño de PCB, primero se deben tener en cuenta la estructura de la placa de circuito y el apilado. Por lo general, el patrón y la forma de la placa de circuito ya se han determinado, y la determinación del número de capas del apilado depende de la frecuencia de la señal y de la densidad de pines de la placa de circuito,Costo de fabricación de PCB, período de fabricación y requisitos de fiabilidad. Las placas de conmutación de interconexión FDR tienen alta frecuencia y densidad, y la aplicación de placas multicapa es el paso necesario para reducir la interferencia. Además, la determinación del número de capas es crucial.

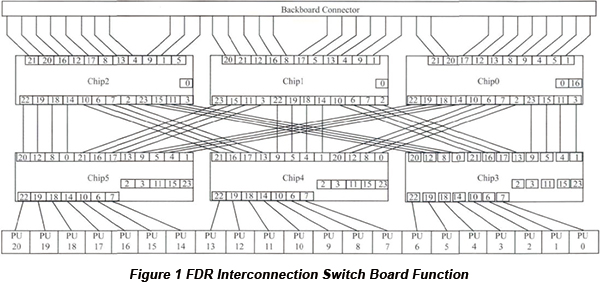

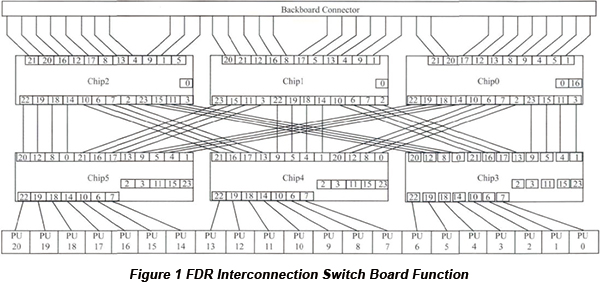

El chip de interconexión FDR tiene 24 puertos y cada puerto dispone de 8 canales Tx y 8 canales Rx en el modo de funcionamiento de acoplamiento mutuo. La placa de interconexión FDR utiliza 6 chips de interconexión y 3 chips de bajada, y se accede a 32 puertos a través del conector de la placa posterior. Los 3 chips de subida acceden a 21 puertos mediante fibras ópticas QSFP (Quad Small Form-factor Pluggable). El chip de subida y el chip de bajada están conectados entre sí a través de 4 puertos, como se muestra en la Figura 1.

FDR presenta el paquete deBGA (Matriz de Bolas)con un área de 50 mm x 50 mm, 1157 pines y un espaciado de 1,0 mm, y los pines P/N en los puertos de Tx y Rx están distribuidos según 3 círculos concéntricos. Teóricamente, se pueden aplicar 3 capas de señal para sacar todos los pines de todos los puertos del BGA. Considerando los dos elementos siguientes, se pueden usar dos capas de señal para acceder a un grupo de pines de círculos concéntricos.

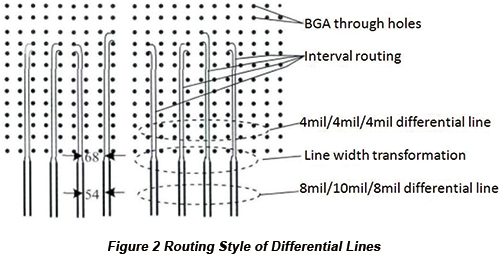

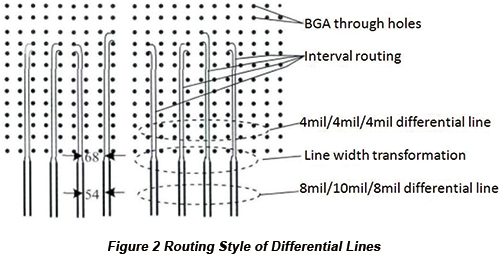

a. Debido a la limitación de espacio, el ancho de línea/espaciado/ancho de las líneas diferenciales es de 4mil/4mil/4mil y se ampliará a 8mil/10mil/8mil al salir del BGA, y la distancia entre pares de líneas diferenciales no debe ser inferior a 50mil. Por lo tanto, un par de líneas diferenciales tiene que ocupar un ancho de 2 mm y 48 pares de señales se encuentran a lo largo del borde con la mayor densidad. Por eso es difícil implementar este método.

b. El espaciado entre los pines BGA es de 1 mm. Si se aplica una capa de señal para acceder a un grupo de señales en círculos concéntricos, el espaciado entre los pares de líneas diferenciales bajo el BGA es de solo 14 mil, lo cual está muy lejos de los 50 mil requeridos. Además, la longitud máxima de ruteo en paralelo es de solo 20 mm, lo que generará cierta diafonía.

Para evitar los factores negativos mencionados anteriormente, se aplican dos capas de señal para acceder a un grupo de señales de círculos concéntricos y, en cada capa de señal, la señal diferencial debe salir del BGA con un espaciado de 50 mil. Por lo tanto, las placas de interconexión FDR requieren al menos 6 capas para sacar todas las señales diferenciales del BGA. Teniendo en cuenta la conectividad y la cantidad de ruteo de la placa, así como suficiente superficie de placa para el condensador de acoplamiento de intercambio, se aplican 8 señales internas y una pila de 22 capas.

Análisis de diafonía y medidas de reducción

La diafonía es la primera consideración en términos de diseño de circuitos de alta velocidad y alta densidad. Cuando el voltaje y la corriente en la línea agresora cambian, se produce un acoplamiento electromagnético a través de la capacitancia mutua y la inductancia mutua entre la línea agresora y la línea víctima. La diafonía que fluye hacia el terminal de transmisión a lo largo de la línea víctima se denomina diafonía de extremo cercano, mientras que la diafonía que fluye hacia el terminal de recepción a lo largo de la línea víctima se denomina diafonía de extremo lejano. En términos generales, el voltaje total de ruido en la línea víctima debe controlarse por debajo del 5% del voltaje de la señal. Lo mejor es controlar el presupuesto de diafonía de una sola línea agresora de flanco dentro del 1%, considerando otras fuentes de ruido y las líneas agresoras alrededor de ambos lados de la línea víctima.

Los puntos clave a seguir en términos de reducción de diafonía incluyen:

a. Se debe aumentar el espacio entre la línea agresora y la línea víctima y reducir la longitud del trazado en paralelo.

b. La tierra integrada se aplica como el camino de retorno de las señales. Según la ley empírica, para la línea strip de 50 Ω, cuando el espaciamiento es tres veces el ancho de la línea, la diafonía de extremo cercano es aproximadamente del 0,5%. Para la línea microstrip de 50 Ω, cuando el espaciamiento es tres veces el ancho de la línea, la diafonía de extremo cercano es aproximadamente del 1%. La diafonía de extremo lejano en líneas strip o en líneas microstrip totalmente embebidas es casi cero, y la polaridad de la diafonía de extremo lejano de las líneas de transmisión microstrip es negativa, con una magnitud relativamente grande porque la influencia del acoplamiento inductivo es mayor que la del acoplamiento capacitivo.

• Enrutamiento por intervalos

En este diseño, la impedancia diferencial de la línea diferencial de alta velocidad es de 100 Ω. Basado en el solucionador de campos Si9000, se calcula que el ancho/separación/ancho de la línea es de 8 mil/10 mil/8 mil. Cuanto más ancha es la línea, menor es la atenuación, y la separación de 10 mil se utiliza para mantener la impedancia diferencial de 100 Ω. Este tipo de línea diferencial se aplica fuera del área del chip BGA. Para disminuir la diafonía, la separación entre dos pares de líneas diferenciales no es inferior a 80 mil. La separación entre pines del chip de interconexión en este artículo es de 1 mm y la limitación del tamaño del orificio pasante del BGA hace que el ancho/separación/ancho de la línea diferencial en el área del chip BGA sea de 4 mil/4 mil/4 mil. Aunque la impedancia diferencial de este tipo de línea diferencial también es de 100 Ω, la pérdida de conducción es grande, lo que requiere que la línea diferencial de 4 mil/4 mil/4 mil se transforme en 8 mil/10 mil/8 mil tan pronto como entre en el área del chip BGA. Para reducir la diafonía, la línea diferencial de 4 mil/4 mil/4 mil en el área del chip BGA aplica el método de enrutamiento intercalado para asegurar que la separación entre dos pares de líneas diferenciales también sea superior a 50 mil, como se muestra en la Figura 2.

• Orificios diferenciales

En este diseño se establecen orificios diferenciales específicos para la aplicación de capacitancia de acoplamiento por intercambio en la capa de superficie de conexión. Es necesario colocar orificios de tierra junto a los orificios diferenciales para proporcionar un canal de retorno para la trayectoria de retorno. El diseño con cuatro orificios de tierra ofrece el mejor efecto, y también se pueden utilizar dos orificios de tierra cuando el área de la placa es limitada. Además, deben adoptarse medidas como el taladrado posterior y la eliminación de pads internos en los orificios diferenciales para reducir el cambio de impedancia en dichos orificios, con el fin de disminuir la diafonía y la reflexión.

• Evitar que Tx y Rx se enruten en la misma capa

Para reducir la diafonía, la línea diferencial de Tx debe rutearse en una capa diferente de la línea diferencial de Rx. Aquí, Tx se refiere al terminal de origen de la línea diferencial, mientras que Rx se refiere al terminal de recepción de la línea diferencial. Si ambas deben rutearse en la misma capa, el espacio entre ellas debe ser superior a 5 mm para garantizar la seguridad.

• Regla de las 20 horas

En el circuito de PCB con alta frecuencia y alta velocidad, la energía de RF se acopla a través de la capa de alimentación y la capa de tierra de la PCB, y se genera una fuga de flujo magnético en el borde entre la capa de alimentación y la capa de tierra. La energía de RF puede radiarse al espacio libre. La regla 20H indica que, si hay corrientes de alta velocidad en la placa, existen campos electromagnéticos asociados a ellas. En el diseño de este artículo, la distancia entre todos los ruteos y el borde de la placa debe ser al menos 20 veces el ancho de la línea, y la distancia entre los orificios diferenciales de alta velocidad y las líneas de corte del plano de alimentación es de al menos 5 mm.

• Enrutamiento en la capa de superficie

En el diseño de PCBs de alta frecuencia, considerando el crosstalk de extremo lejano relativamente grande entre microstrip y strip lines, se prohíbe el uso de líneas diferenciales de alta velocidad en la capa superficial. En el diseño de este artículo, se requieren como máximo 8 capas internas de ruteo debido a las limitaciones del proceso de fabricación. Además, la limitación en la disposición de terminales del chip de interconexión hace imposible que solo las capas internas implementen las conexiones de las líneas diferenciales de interconexión entre los 6 chips dentro de la placa de conexión.

.

. .

.