De nos jours, le débit de transmission du réseau d’interconnexion des ordinateurs haute performance, avec l’application de la transmission série à haute vitesse, a évolué jusqu’au FDR (Fourteen Data Rate, 14 Gb/s), la 4ᵉ génération après le SDR initial (Single Data Rate, 2,5 Gb/s), le DDR (Double Data Rate, 5 Gb/s) et le QDR (Quad Data Rate, 10 Gb/s). La conception du PCB (Circuit imprimé) avec les cartes d’interconnexion, de commutation et d’interface, qui sont essentielles à la formation d’Internet, est entrée dans le domaine FDR à haute vitesse et haute fréquence. Comme le temps de montée du signal FDR a été drastiquement réduit à l’ordre de 10 ps, une série de problèmes concernant l’intégrité du signal est devenue le facteur clé pour déterminer la possibilité de mise en œuvre fonctionnelle et de fonctionnement fiable, tels que l’atténuation, la diaphonie, la réflexion, les interférences électromagnétiques, etc. En raison des caractéristiques des puces d’interconnexion FDR, comprenant de multiples ports, de multiples canaux, de multiples catégories d’alimentation et une forte consommation d’énergie, plusieurs puces d’interconnexion doivent toujours être intégrées sur une seule carte d’interconnexion afin d’augmenter le débit. Sur une carte à l’espace limité, d’une part, certaines exigences doivent être satisfaites, notammentdisposition des composantset la dissipation de chaleur, le routage à haute densité, la transmission sur de longues distances à l’arrière de la carte et l’intégrité de toutes sortes de signaux. D’un autre côté, certains éléments doivent être pris en considération, notamment la durée de conception du PCB, les limitations des techniques de fabrication du PCB et le contrôle des coûts. Par conséquent, la mise en œuvre de la conception et la vérification par simulation sont extrêmement difficiles. Sur la base d’un exemple de conception de PCB d’interconnexion FDR et de carte de commutation, cet article propose quelques méthodes d’optimisation en termes de sélection du matériau de substrat,conception d’empilement, règles de routage et conception anti-interférences afin de résoudre le problème d’intégrité de toutes sortes de signaux dans le processus de conception de PCB haute vitesse FDR.

Sélection de l’attribut d’atténuation et du matériau de substrat

Pour les signaux FDR à haute fréquence, la perte de ligne de transmission est le problème qui concerne l’intégrité du signal. Lorsque les signaux FDR sont transmis du terminal émetteur au terminal récepteur le long des canaux d’interconnexion, en raison du fait que l’atténuation haute fréquence est bien plus importante que l’atténuation basse fréquence, une grave déformation se produit sur la forme d’onde du signal arrivant au terminal récepteur. La déformation se classe principalement en deux aspects : l’amplitude de tension des signaux a fortement diminué, tandis qu’une forte dégradation s’est produite sur le front montant du signal. La première limite la distance de transmission des signaux, tandis que la seconde entraîne des interférences entre les codes. La perte de ligne de transmission A peut être considérée comme la somme de la perte de conducteurAcondet perte diélectriqueAdielcomme indiqué dans la formule (1) :A=Adiel+Acond.

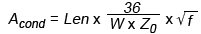

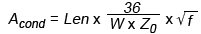

La perte de conducteur fait référence à la perte causée par la résistance série sur le conducteur en cuivre entre le trajet du signal et le trajet de retour. En situation de haute fréquence, l’effet de peau fait circuler le courant à la surface des conducteurs en cuivre environnants. Avec l’augmentation de la résistance série équivalente des conducteurs en cuivre, la perte de conducteur augmente avec la fréquence, de manière proportionnelle à la racine carrée de la fréquence, comme illustré dans la formule (2) : .

.

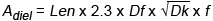

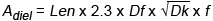

La perte diélectrique désigne la perte générée par le milieu du matériau de substrat, principalement déterminée par les propriétés du matériau et indépendante de la structure géométrique, y compris la largeur du conducteur, proportionnelle à la fréquence, comme indiqué dans la formule (3) : .

.

Sur la base de la formule (2), l’augmentation de la largeur de la ligne est capable de réduire les pertes du conducteur. Cependant, dans la pratiqueConception de PCBla largeur des conducteurs ne peut jamais être indéfiniment grande en raison des limitations de l’espacement entre les broches, de la carte, du nombre de couches de signaux et de l’impédance. La largeur/espacement/largeur de conducteur couramment appliquée dans la conception FDR est généralement de 7 mil/7 mil/7 mil ou 8 mil/10 mil/8 mil. Lorsque la largeur du conducteur est identique, la perte de conducteur est proportionnelle à la longueur du conducteur, sans aucun lien avec le matériau. Par conséquent, pour réduire la perte de transmission globale, seule la perte diélectrique doit être prise en considération. D’après la formule (3), la perte diélectrique est proportionnelle au facteur de dissipation et l’utilisation de faibles facteurs de dissipation peut contribuer à la réduction de la perte diélectrique, entraînant la diminution de la perte de transmission globale.

Le tableau 1 répertorie les paramètres d’attributs de trois matériaux ordinaires de cartes haute vitesse et les valeurs de perte calculées selon les formules (1), (2) et (3) lorsque le débit de transmission est de 14 Gb/s, la largeur du conducteur de 8 mil et l’impédance de 50 Ω.

|

Paramètres du matériau de la carte

|

FR4

|

Nelco4000-13SI

|

Megtron6

|

| Df@10GHz |

0,02 |

0,008 |

0,004 |

| Dk@10GHz |

4,10 |

3,200 |

3,600 |

| Acond@7GHz/in |

0,24 |

0,240 |

0,240 |

| Adiel@7GHz/in |

0,65 |

0,230 |

0,120 |

| A@7GHz/po |

0,89 |

0,470 |

0,360 |

| A@7GHz/30po |

27,00 |

14.000 |

11 000 |

| Coût relatif |

1,00 |

3,500 |

8,000 |

On peut indiquer qu’avec un débit de transmission de 14 Gb/s et une longueur de transmission de 30 pouces, la perte de transmission globale du Nelco4000-13SI est d’environ 14 dB, tandis que l’atténuation de l’amplitude de tension qu’une puce FDR typique peut supporter se situe dans une plage de 20 dB à 25 dB. Par conséquent, ce type de matériau de carte peut être utilisé dans la conception de cartes de commutation d’interconnexion FDR avec une distance de transmission inférieure à 30 pouces. Cependant, l’atténuation de transmission globale du FR4 est d’environ 27 dB et le FR4 ne peut pas être utilisé pour la conception FDR de longue distance, mais pour les cartes d’interface d’interconnexion FDR avec une courte distance de transmission, il est possible de choisir le FR4 afin de réduire les coûts. Quant au Megtron6, dont l’atténuation de transmission globale est la plus faible, il présente le coût le plus élevé et son application dans le FDR entraîne une augmentation des coûts de l’architecture système. En conclusion, pourPCB haute fréquence, le matériau de la carte est la base, et le choix du matériau de la carte détermine la longueur de transmission des signaux.

Conception de disposition et d’empilement

Pour la conception de circuits imprimés, la structure et l’empilage de la carte doivent d’abord être pris en considération. En général, le motif et la forme de la carte de circuit ont déjà été déterminés, et la détermination du nombre de couches d’empilage dépend de la fréquence du signal et de la densité des broches de la carte de circuit,Coût de fabrication des circuits imprimés, période de fabrication et exigences de fiabilité. Les cartes de commutation d’interconnexion FDR présentent une haute fréquence et une grande densité, et l’utilisation de cartes multicouches est une étape nécessaire pour réduire les interférences. De plus, la détermination du nombre de couches est cruciale.

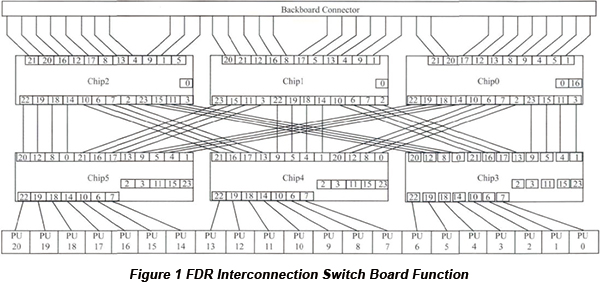

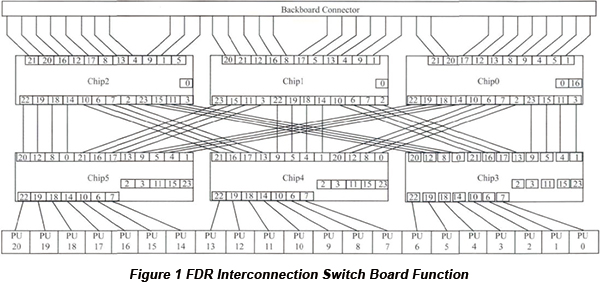

La puce d’interconnexion FDR comporte 24 ports et chaque port dispose de 8 canaux Tx et 8 canaux Rx en mode de fonctionnement par intercouplage. La carte d’interconnexion FDR utilise 6 puces d’interconnexion et 3 puces de liaison descendante, et 32 ports sont accessibles via le connecteur de fond de panier. Les 3 puces de liaison montante accèdent à 21 ports via des fibres optiques QSFP (Quad Small Form-factor Pluggable). La puce de liaison montante et la puce de liaison descendante sont connectées l’une à l’autre par 4 ports, comme illustré à la Figure 1.

FDR comprend le package deBGA (Boîtier à billes)avec une surface de 50 mm x 50 mm, 1157 broches et un espacement de 1,0 mm, les broches P/N aux ports Tx et Rx sont réparties selon 3 cercles concentriques. Théoriquement, 3 couches de signaux peuvent être appliquées pour faire sortir toutes les broches de tous les ports du BGA. En tenant compte des deux éléments suivants, deux couches de signaux peuvent être utilisées pour accéder à un groupe de broches de cercles concentriques.

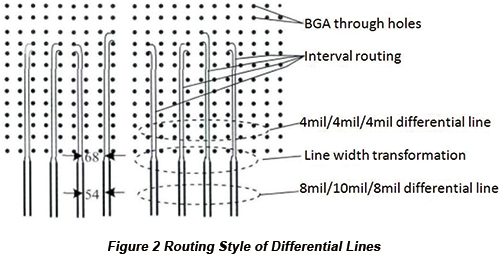

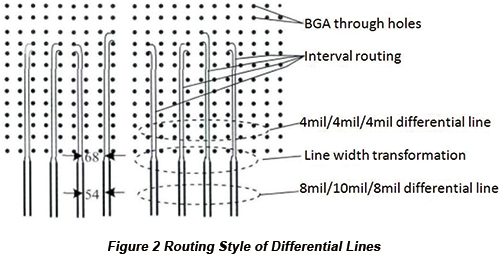

a. En raison de la limitation de l’espace, la largeur / l’espacement / la largeur des lignes différentielles est de 4 mil / 4 mil / 4 mil et elle sera portée à 8 mil / 10 mil / 8 mil en sortant du BGA, et la distance entre les paires de lignes différentielles ne doit pas être inférieure à 50 mil. Par conséquent, une paire de lignes différentielles doit occuper une largeur de 2 mm et 48 paires de signaux se trouvent le long du bord présentant la plus grande densité. Il est donc difficile de mettre en œuvre cette méthode.

b. L’espacement entre les broches du BGA est de 1 mm. Si une couche de signal est utilisée pour accéder à un groupe de signaux en cercles concentriques, l’espacement entre les paires de lignes différentielles sous le BGA n’est que de 14 mil, ce qui est très inférieur aux 50 mil requis. De plus, la longueur maximale de routage parallèle n’est que de 20 mm, ce qui générera un certain diaphonie.

Pour éviter les facteurs négatifs mentionnés ci-dessus, deux couches de signaux sont appliquées pour accéder à un groupe de signaux de cercles concentriques et le signal différentiel de chaque couche de signaux doit être conduit hors du BGA selon un espacement de 50 mil. Par conséquent, au moins 6 couches sont requises pour que les cartes d’interconnexion FDR fassent sortir tous les signaux différentiels du BGA. En tenant compte de la connectivité et de la quantité de routage de la carte ainsi que de la surface de carte suffisante pour le condensateur de couplage d’échange, 8 couches de signaux internes et une empilisation de 22 couches sont appliquées.

Analyse de diaphonie et mesures de réduction

La diaphonie est la première considération en matière de conception de circuits à haute vitesse et haute densité. Lorsque la tension et le courant de la ligne perturbatrice varient, un couplage électromagnétique se produit par la capacité mutuelle et l’inductance mutuelle entre la ligne perturbatrice et la ligne victime. La diaphonie se propageant vers le terminal d’émission le long de la ligne victime est appelée diaphonie de proximité, tandis que la diaphonie se propageant vers le terminal de réception le long de la ligne victime est appelée diaphonie de distance. De manière générale, la tension de bruit globale sur la ligne victime doit être maintenue en dessous de 5 % de la tension du signal. Il est préférable de limiter le budget de diaphonie d’une seule ligne perturbatrice à front unique à 1 %, en tenant compte des autres sources de bruit et des lignes perturbatrices situées de part et d’autre de la ligne victime.

Les points clés à suivre en matière de réduction de diaphonie comprennent :

a. L’espacement entre la ligne perturbatrice et la ligne victime doit être augmenté et la longueur de routage parallèle doit être réduite.

b. La masse intégrée est utilisée comme chemin de retour des signaux. Selon la loi empirique, pour une ligne en bande de 50 Ω, lorsque l’espacement est trois fois la largeur de la ligne, la diaphonie en bout proche est d’environ 0,5 %. Pour une microbande de 50 Ω, lorsque l’espacement est trois fois la largeur de la ligne, la diaphonie en bout proche est d’environ 1 %. La diaphonie en bout éloigné sur les lignes en bande ou sur les microbandes entièrement enfouies est presque nulle, et la polarité de la diaphonie en bout éloigné des lignes de transmission en microbande est négative, avec une amplitude relativement importante, car l’influence du couplage inductif est plus grande que celle du couplage capacitif.

• Routage par intervalles

Dans cette conception, l’impédance différentielle de la ligne différentielle haute vitesse est de 100 Ω. Sur la base du solveur de champ Si9000, la largeur d’une piste / l’espacement / la largeur d’une piste sont calculés à 8 mil / 10 mil / 8 mil. Plus la piste est large, plus l’atténuation est faible, et l’espacement de 10 mil permet de maintenir l’impédance différentielle de 100 Ω. Ce type de ligne différentielle est utilisé en dehors de la zone de puce BGA. Afin de réduire la diaphonie, l’espacement entre deux paires de lignes différentielles n’est pas inférieur à 80 mil. L’espacement entre les broches du circuit d’interconnexion dans cet article est de 1 mm et la limitation de la taille des trous traversants du BGA fait que la largeur / l’espacement / la largeur de la ligne différentielle dans la zone de puce BGA est de 4 mil / 4 mil / 4 mil. Bien que l’impédance différentielle de ce type de ligne différentielle soit également de 100 Ω, la perte de conduction est importante, ce qui nécessite que la ligne différentielle de 4 mil / 4 mil / 4 mil soit transformée en 8 mil / 10 mil / 8 mil dès qu’elle entre dans la zone de puce BGA. Afin de réduire la diaphonie, la ligne différentielle de 4 mil / 4 mil / 4 mil dans la zone de puce BGA adopte un routage alterné pour garantir que l’espacement entre deux paires de lignes différentielles soit également supérieur à 50 mil, comme illustré à la Figure 2.

• Trous différentiels

Des trous différentiels spécifiques sont prévus dans cette conception pour l’application de la capacité de couplage d’échange sur la couche de surface de connexion. Des trous de masse doivent être placés à côté des trous différentiels afin de fournir un canal de retour pour le chemin de retour. La conception avec quatre trous de masse offre le meilleur effet, et deux trous de masse peuvent également être utilisés lorsque la surface de la carte est limitée. En outre, des mesures telles que le backdrilling et la suppression des pastilles internes doivent être appliquées aux trous différentiels afin de réduire la variation d’impédance au niveau de ces trous, dans le but de diminuer la diaphonie et la réflexion.

• Empêcher que Tx et Rx soient acheminés dans la même couche

Afin de réduire la diaphonie, la ligne différentielle Tx doit être routée sur une couche différente de la ligne différentielle Rx. Ici, Tx fait référence à la borne source de la ligne différentielle tandis que Rx fait référence à la borne de réception de la ligne différentielle. Si elles doivent toutes deux être routées sur la même couche, l’espacement entre elles doit être supérieur à 5 mm pour garantir la sécurité.

• règle des 20 heures

Dans les circuits imprimés à haute fréquence et à haute vitesse, l’énergie RF est couplée par le plan d’alimentation et le plan de masse du PCB, et une fuite de flux magnétique de bord est générée entre le plan d’alimentation et le plan de masse. L’énergie RF radio peut être rayonnée dans l’espace libre. La règle des 20H indique que s’il y a des courants à haute vitesse sur la carte, il existe des champs électromagnétiques qui leur sont associés. Dans la conception de cet article, la distance entre tous les tracés et le bord de la carte doit être au moins 20 fois la largeur de la piste, et la distance entre les vias différentiels à haute vitesse et les lignes de coupure du plan d’alimentation est d’au moins 5 mm.

• Routage sur la couche de surface

Dans la conception de circuits imprimés haute fréquence, étant donné le diaphonie de bout de ligne relativement importante entre les microstrips et les striplines, les lignes différentielles à haute vitesse sont interdites sur la couche de surface. Dans la conception présentée dans cet article, un maximum de 8 couches de routage internes est requis en raison des limitations du procédé de fabrication. De plus, la contrainte de disposition des broches du circuit d’interconnexion rend impossible l’utilisation exclusive des couches internes pour réaliser les connexions des lignes différentielles d’interconnexion entre les 6 puces à l’intérieur de la carte d’interconnexion.

.

. .

.