Al giorno d’oggi, la velocità di trasmissione delle reti di interconnessione per computer ad alte prestazioni con l’applicazione della trasmissione seriale ad alta velocità si è evoluta fino a FDR (Fourteen Data Rate, 14 Gb/s), la quarta generazione dopo la SDR (Single Data Rate, 2,5 Gb/s) iniziale, la DDR (Double Data Rate, 5 Gb/s) e la QDR (Quad Data Rate, 10 Gb/s). La progettazione del PCB (Circuito stampato) con scheda di interconnessione e di commutazione e schede di interfaccia, che sono essenziali per la formazione di Internet, è entrato nel campo FDR ad alta velocità e alta frequenza. Poiché il tempo di salita del segnale FDR si è drasticamente ridotto all’ordine di grandezza dei 10 ps, una serie di problemi riguardanti l’integrità del segnale è diventata la caratteristica chiave per determinare la possibilità di implementazione delle funzionalità e di funzionamento affidabile, come attenuazione, diafonia, riflessione, interferenza elettromagnetica ecc. Sulla base delle caratteristiche dei chip di interconnessione FDR, tra cui porte multiple, canali multipli, categorie di alimentazione multiple e alto consumo energetico, è sempre necessario integrare più chip di interconnessione su un’unica scheda di interconnessione per aumentare il tasso di throughput. Su una scheda con spazio limitato, da un lato, devono essere soddisfatti alcuni requisiti, tra cuilayout del componentedissipazione del calore, instradamento ad alta densità, trasmissione a lunga distanza sul retro della scheda e integrità di tutti i tipi di segnali. D’altra parte, devono essere presi in considerazione alcuni elementi, tra cui il periodo di progettazione del PCB, i limiti delle tecniche di fabbricazione del PCB e il controllo dei costi. Pertanto, l’implementazione del progetto e la verifica tramite simulazione risultano estremamente difficili. Sulla base di un esempio di progettazione PCB di interconnessione FDR e scheda di commutazione, questo articolo propone alcuni metodi di ottimizzazione in termini di selezione del materiale del substrato,progettazione dello stack, regole di instradamento e progettazione anti-interferenza al fine di risolvere il problema di integrità di tutti i tipi di segnali nel processo di progettazione PCB ad alta velocità FDR.

Selezione dell'attributo di attenuazione e del materiale del substrato

Per i segnali FDR ad alta frequenza, la perdita nella linea di trasmissione è il problema che riguarda l’integrità del segnale. Quando i segnali FDR vengono trasmessi dal terminale trasmittente al terminale ricevente lungo i canali di interconnessione, poiché l’attenuazione alle alte frequenze è molto maggiore di quella alle basse frequenze, si verifica una grave deformazione della forma d’onda del segnale che arriva al terminale ricevente. La deformazione è principalmente classificata in due aspetti: l’ampiezza di tensione dei segnali è notevolmente diminuita, mentre si è verificato un forte degrado del fronte di salita del segnale. Il primo limita la distanza di trasmissione dei segnali, mentre il secondo porta a interferenze tra i codici. La perdita della linea di trasmissione A può essere considerata come la somma della perdita del conduttoreAconde perdita dielettricaAdielcome mostrato nella Formula (1):A=Adiel+Acond.

La perdita del conduttore si riferisce alla perdita causata dal resistore in serie sul conduttore di rame tra il percorso del segnale e il percorso di ritorno. In condizioni di alta frequenza, l’effetto pelle fa sì che la corrente fluisca sulla superficie dei conduttori di rame circostanti. Con l’aumento della resistenza equivalente in serie dei conduttori di rame, la perdita del conduttore aumenterà con l’aumentare della frequenza, che è direttamente proporzionale alla radice quadrata della frequenza, come illustrato nella Formula (2): .

.

La perdita dielettrica si riferisce alla perdita generata dal mezzo del materiale del substrato, determinata principalmente dalle proprietà del materiale e non correlata alla struttura geometrica, inclusa la larghezza del conduttore, ed è proporzionale in modo diretto alla frequenza, come mostrato nella Formula (3): .

.

In base alla Formula (2), l’aumento della larghezza della linea è in grado di ridurre la perdita del conduttore. Tuttavia, nella praticaProgettazione PCB, la larghezza dei conduttori non può mai essere indefinitamente ampia a causa dei limiti di spaziatura tra i pin, della scheda, del numero di strati di segnale e dell’impedenza. La larghezza/spaziatura/larghezza dei conduttori comunemente applicata nella progettazione FDR è solitamente 7mil/7mil/7mil o 8mil/10mil/8mil. A parità di larghezza del conduttore, la perdita del conduttore è direttamente proporzionale alla lunghezza del conduttore, senza alcuna relazione con il materiale. Pertanto, per ridurre la perdita complessiva di trasmissione, è necessario considerare solo la perdita dielettrica. In base alla Formula (3), la perdita dielettrica è proporzionale al fattore di dissipazione e l’applicazione di fattori di dissipazione ridotti può contribuire alla diminuzione della perdita dielettrica, portando alla riduzione della perdita complessiva di trasmissione.

La Tabella 1 elenca i parametri delle proprietà di tre comuni materiali per schede ad alta velocità e i valori di perdita calcolati secondo le formule (1), (2) e (3) quando la velocità di trasmissione è 14 Gb/s, la larghezza del conduttore è 8 mil e l’impedenza è 50 Ω.

|

Parametri del materiale della scheda

|

FR4

|

Nelco4000-13SI

|

Megtron6

|

| Df@10GHz |

0,02 |

0,008 |

0,004 |

| Dk@10GHz |

4,10 |

3.200 |

3.600 |

| Acond@7GHz/in |

0,24 |

0,240 |

0,240 |

| Adiel@7GHz/in |

0,65 |

0,230 |

0,120 |

| A@7GHz/in |

0,89 |

0,470 |

0,360 |

| A@7GHz/30in |

27,00 |

14.000 |

11.000 |

| Costo relativo |

1,00 |

3.500 |

8.000 |

Si può indicare che, con una velocità di trasmissione di 14 Gb/s e una lunghezza di trasmissione di 30 pollici, la perdita di trasmissione complessiva del Nelco4000-13SI è di circa 14 dB, mentre l’attenuazione dell’ampiezza di tensione che un tipico chip FDR può sopportare è nell’intervallo da 20 dB a 25 dB. Pertanto, questo tipo di materiale per circuiti stampati può essere applicato nella progettazione di schede di commutazione per interconnessioni FDR con una distanza di trasmissione inferiore a 30 pollici. Tuttavia, l’attenuazione complessiva di trasmissione del FR4 è di circa 27 dB e il FR4 non può essere utilizzato per la progettazione FDR su lunghe distanze, ma per le schede di interfaccia di interconnessione FDR con brevi distanze di trasmissione è possibile scegliere il FR4 per ridurre i costi. Per quanto riguarda il Megtron6, la cui attenuazione complessiva di trasmissione è la più bassa, esso presenta il costo più elevato e il suo impiego nell’FDR porta a un aumento dei costi dell’architettura di sistema. In conclusione, perPCB ad alta frequenza, il materiale della scheda è la base e la selezione del materiale della scheda determina la lunghezza di trasmissione dei segnali.

Progettazione del layout e dello stack

Per la progettazione PCB, è necessario innanzitutto prendere in considerazione la struttura e lo stack della scheda. Di solito, il pattern e la forma della scheda sono già stati determinati e la determinazione del numero di strati dipende dalla frequenza del segnale, dalla densità dei pin della scheda,Costo di fabbricazione PCB, periodo di produzione e requisiti di affidabilità. Le schede di commutazione di interconnessione FDR presentano alta frequenza e densità e l’applicazione di schede multistrato è il passo necessario per ridurre le interferenze. Inoltre, la determinazione del numero di strati è cruciale.

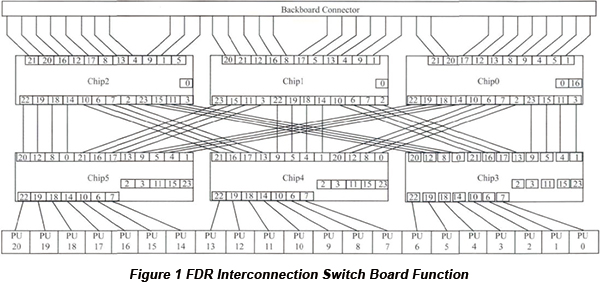

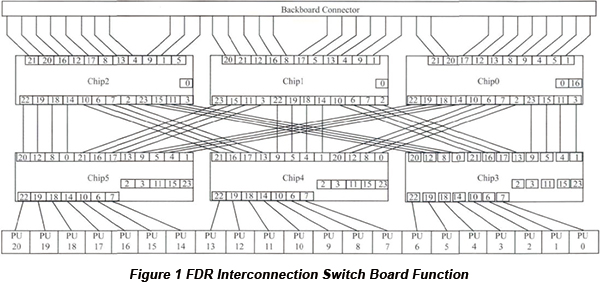

Sul chip di interconnessione FDR sono presenti 24 porte e ciascuna porta dispone di 8 canali Tx e 8 canali Rx nel metodo di funzionamento ad intercoupling. La scheda di interconnessione FDR utilizza 6 chip di interconnessione e 3 chip di downlink e 32 porte sono accessibili tramite il connettore di backplane. I 3 chip di uplink accedono a 21 porte tramite fibre ottiche QSFP (Quad Small Form-factor Pluggable). Il chip di uplink e il chip di downlink sono collegati tra loro tramite 4 porte, come mostrato in Figura 1.

FDR include il pacchetto diBGA (Ball Grid Array)con un'area di 50 mm x 50 mm, 1157 pin e una spaziatura di 1,0 mm, i pin P/N alle porte di Tx e Rx sono distribuiti secondo 3 cerchi concentrici. Teoricamente, si possono applicare 3 strati di segnale per portare tutti i pin di tutte le porte fuori dal BGA. Considerando i due elementi seguenti, è possibile utilizzare due strati di segnale per accedere a un gruppo di pin dei cerchi concentrici.

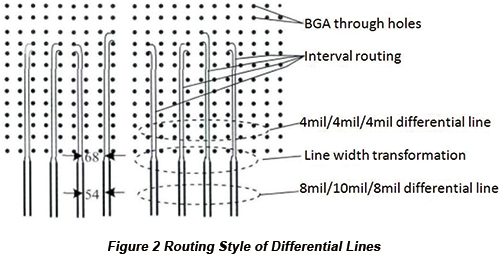

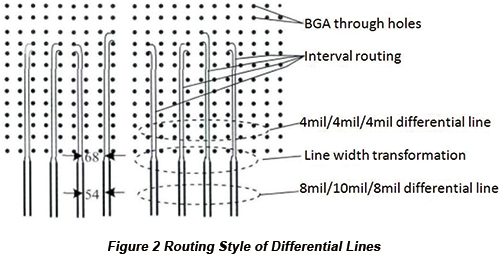

a. A causa della limitazione dello spazio, la larghezza/spaziatura/larghezza delle linee differenziali è di 4mil/4mil/4mil e verrà ampliata a 8mil/10mil/8mil uscendo dal BGA, e la distanza tra le coppie di linee differenziali non deve essere inferiore a 50mil. Pertanto, una coppia di linee differenziali deve occupare una larghezza di 2 mm e 48 coppie di segnali si trovano lungo il bordo con la massima densità. Di conseguenza, è difficile implementare questo metodo.

b. La spaziatura tra i pin BGA è di 1 mm. Se si utilizza uno strato di segnale per accedere a un gruppo di segnali a cerchi concentrici, la spaziatura tra le coppie di linee differenziali sotto il BGA è di soli 14 mil, molto inferiore ai 50 mil richiesti. Inoltre, la lunghezza massima di instradamento in parallelo è di soli 20 mm, il che genererà un certo crosstalk.

Per evitare i fattori negativi sopra menzionati, vengono applicati due strati di segnale per accedere a un gruppo di segnali a cerchi concentrici e il segnale differenziale in ciascuno strato di segnale deve essere portato fuori dal BGA secondo una spaziatura di 50 mil. Pertanto, sono necessari almeno 6 strati per le schede di interconnessione FDR affinché tutti i segnali differenziali siano portati fuori dal BGA. Considerando la connettività e la quantità di instradamento della scheda e una superficie sufficiente per i condensatori di accoppiamento in derivazione, vengono applicati 8 strati interni di segnale e uno stack di 22 strati.

Analisi della diafonia e misure di riduzione

La diafonia è la prima considerazione nella progettazione di circuiti ad alta velocità e alta densità. Quando la tensione e la corrente nella linea disturbante cambiano, si verifica un accoppiamento elettromagnetico attraverso la mutua capacità e la mutua induttanza tra la linea disturbante e la linea vittima. La diafonia che fluisce verso il terminale di trasmissione lungo la linea vittima è chiamata diafonia di estremità vicina, mentre la diafonia che fluisce verso il terminale di ricezione lungo la linea vittima è chiamata diafonia di estremità lontana. In generale, la tensione di rumore complessiva sulla linea vittima dovrebbe essere mantenuta al di sotto del 5% della tensione del segnale. È preferibile controllare il budget di diafonia della singola transizione della linea disturbante entro l’1%, tenendo conto delle altre sorgenti di rumore e delle linee disturbanti sui due lati della linea vittima.

I punti chiave da seguire in termini di riduzione del crosstalk includono:

a. La distanza tra la linea aggressiva e la linea vittima dovrebbe essere aumentata e la lunghezza del percorso parallelo dovrebbe essere ridotta.

b. La massa integrata viene utilizzata come percorso di ritorno dei segnali. Secondo la legge empirica, per una stripline da 50 Ω, quando la spaziatura è tre volte la larghezza della linea, il diafonia di near-end è approssimativamente dello 0,5%. Per una microstrip line da 50 Ω, quando la spaziatura è tre volte la larghezza della linea, il diafonia di near-end è approssimativamente dell’1%. Il diafonia di far-end sulle stripline o sulle microstrip completamente incapsulate è quasi zero e la polarità del diafonia di far-end delle linee di trasmissione microstrip è negativa, con un’ampiezza relativamente grande perché l’influenza dell’accoppiamento induttivo è maggiore di quella dell’accoppiamento capacitivo.

• Instradamento per intervalli

In questo progetto, l’impedenza differenziale della linea differenziale ad alta velocità è di 100 Ω. In base al field solver Si9000, la larghezza/spaziatura/larghezza della linea è calcolata in 8 mil/10 mil/8 mil. Quanto più ampia è la linea, tanto minore è l’attenuazione, e la spaziatura di 10 mil serve a mantenere l’impedenza differenziale di 100 Ω. Questo tipo di linea differenziale è applicato all’esterno dell’area del chip BGA. Per ridurre il crosstalk, la spaziatura tra due coppie di linee differenziali non è inferiore a 80 mil. La spaziatura tra i pin del chip di interconnessione in questo articolo è di 1 mm e il limite di dimensione dei fori passanti del BGA fa sì che la larghezza/spaziatura/larghezza della linea differenziale nell’area del chip BGA sia 4 mil/4 mil/4 mil. Sebbene l’impedenza differenziale di questo tipo di linea differenziale sia anch’essa di 100 Ω, la perdita di conduzione è elevata, richiedendo che la linea differenziale di 4 mil/4 mil/4 mil venga trasformata in 8 mil/10 mil/8 mil non appena entra nell’area del chip BGA. Per ridurre il crosstalk, la linea differenziale di 4 mil/4 mil/4 mil nell’area del chip BGA adotta un instradamento alternato per garantire che la spaziatura tra due coppie di linee differenziali sia anch’essa superiore a 50 mil, come mostrato in Figura 2.

• Fori differenziali

In questo progetto vengono predisposti fori differenziali specifici per l’applicazione della capacità di accoppiamento per scambio sullo strato di connessione superficiale. I fori di massa devono essere posizionati accanto ai fori differenziali per fornire un canale di ritorno per il percorso di ritorno. La progettazione con quattro fori di massa offre l’effetto migliore e si possono utilizzare anche due fori di massa quando l’area della scheda è limitata. Inoltre, sui fori differenziali devono essere adottate misure quali il back drilling e l’eliminazione dei pad interni per ridurre la variazione di impedenza nei fori differenziali, in modo da diminuire diafonia e riflessione.

• Impedire che Tx e Rx vengano instradati nello stesso strato

Per ridurre il crosstalk, la linea differenziale Tx dovrebbe essere instradata in un livello diverso rispetto alla linea differenziale Rx. Qui, Tx si riferisce al terminale sorgente della linea differenziale, mentre Rx si riferisce al terminale ricevente della linea differenziale. Se entrambe devono essere instradate nello stesso livello, la distanza tra di esse deve essere superiore a 5 mm per garantire la sicurezza.

• Regola delle 20 ore

Nel circuito PCB ad alta frequenza e alta velocità, l’energia RF viene accoppiata dallo strato di alimentazione e dallo strato di massa del PCB e si genera una dispersione di flusso magnetico ai bordi tra lo strato di alimentazione e lo strato di massa. L’energia RF irradiata può essere emessa nello spazio libero. La regola del 20H indica che, se sulla scheda sono presenti correnti ad alta velocità, esistono campi elettromagnetici ad esse associati. Nel progetto descritto in questo articolo, la distanza tra tutte le piste e il bordo della scheda deve essere almeno 20 volte la larghezza della traccia e la distanza tra i fori differenziali ad alta velocità e le linee di interruzione del piano di alimentazione è di almeno 5 mm.

• Instradamento sul layer di superficie

Nella progettazione di PCB ad alta frequenza, considerando il relativamente elevato diafonia di estremità lontana tra linee microstrip e stripline, è vietato instradare linee differenziali ad alta velocità sullo strato superficiale. Nella progettazione descritta in questo articolo, sono necessari al massimo 8 strati interni di instradamento a causa dei limiti del processo di produzione. Inoltre, il vincolo di disposizione dei terminali del chip di interconnessione rende impossibile utilizzare esclusivamente gli strati interni per realizzare le connessioni delle linee differenziali di interconnessione tra i 6 chip all’interno della scheda di connessione.

.

. .

.