近年、高速シリアル伝送の適用により、高性能コンピュータ相互接続ネットワークの伝送レートは、初期の SDR(Single Data Rate, 2.5Gb/s)、DDR(Double Data Rate, 5Gb/s)、QDR(Quad Data Rate, 10Gb/s)から第4世代である FDR(Fourteen Data Rate, 14Gb/s)へと発展してきた。PCB(プリント基板)の設計はプリント基板インターネットを構成するうえで不可欠な相互接続およびスイッチボード、インターフェースカードは、FDR の高速・高周波分野に参入している。FDR 信号の立ち上がり時間が 10ps オーダーまで大幅に短縮されたため、減衰、クロストーク、反射、電磁干渉など、信号完全性に関する一連の問題が、機能実現の可否および信頼性の高い動作を左右する主要な要因となっている。多ポート、多チャネル、多電源カテゴリ、高消費電力といった FDR 相互接続チップの特性に基づき、スループットを向上させるためには、複数の相互接続チップを 1 枚の相互接続ボード上に統合する必要がある。限られたスペースのボード上では、一方で、次のような要件を満たさなければならない。コンポーネントレイアウト放熱、高密度配線、基板背面を横断する長距離伝送、およびあらゆる種類の信号の完全性である。一方で、PCB 設計期間、PCB 製造技術の制約、コスト管理などの要素も考慮しなければならない。したがって、設計実装およびシミュレーション検証は極めて困難である。FDR インターコネクションおよびスイッチボードの PCB 設計例に基づき、本稿では基板材料の選定という観点からいくつかの最適化手法を提示する。スタックアップ設計FDR 高速 PCB 設計の過程において、あらゆる信号の完全性の問題を解決するために、配線ルールおよび耐干渉設計を行う。

減衰特性および基板材料の選定

FDR の高周波信号に対しては、伝送線路損失がシグナルインテグリティに関わる問題となる。FDR 信号が送信端から受信端へとインターコネクションチャネルに沿って伝送される際、高周波減衰が低周波減衰よりもはるかに大きいため、受信端に到達する信号波形には深刻な歪みが生じている。この歪みは主に 2 つの側面に分類される。1 つは信号の電圧スイングが大きく低下することであり、もう 1 つは信号の立ち上がりエッジが大きく劣化することである。前者は信号の伝送距離を制限し、後者は符号間干渉を引き起こす。伝送線路損失 A は、導体損失の総和と見なすことができる。Aコンデンサーおよび誘電損失Aダイエル式(1)に示すように:A=Aダイエル+Aコンデンサー。

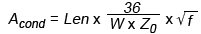

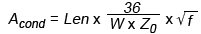

導体損失とは、信号経路とリターン経路の間の銅導体上に直列に存在する抵抗によって生じる損失を指す。高周波の状況では、表皮効果により電流は周囲の銅導体の表面を流れる。銅導体の等価直列抵抗が増加するにつれて、導体損失は周波数の増加とともに上昇し、その増加は周波数の平方根に正比例する。この関係は式(2)に示されている。 。

。

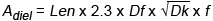

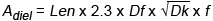

誘電損失とは、基板材料の媒体によって生じる損失を指し、主に材料の特性によって決まり、導体幅を含む幾何学的構造とは無関係であり、周波数に正比例します。これは式(3)に示されています。 。

。

式(2)に基づくと、線幅の増加は導体損失を低減することが可能である。しかし、実際の場面ではPCB設計導体の幅は、ピン間隔、基板、信号層数およびインピーダンスの制約により、無制限に広くすることはできません。FDR 設計で一般的に用いられる導体の幅/間隔/幅は、通常 7mil/7mil/7mil または 8mil/10mil/8mil です。導体幅が同じであれば、導体損失は導体長に正比例し、材料とは無関係です。したがって、全体の伝送損失を低減するためには、誘電体損失のみを考慮すればよいことになります。式(3)に基づけば、誘電体損失は損失係数に比例し、小さな損失係数を用いることで誘電体損失を低減でき、その結果、全体の伝送損失を低減することができます。

表1には、3種類の一般的な高速基板材料の属性パラメータと、伝送速度14Gb/s、導体幅8mil、インピーダンス50Ωの場合に式(1)、(2)、(3)に基づいて算出した損失値を示す。

|

ボード材料パラメータ

|

FR4

|

Nelco4000-13SI

|

Megtron6

|

| Df@10GHz |

0.02 |

0.008 |

0.004 |

| Dk@10GHz |

4.10 |

3.200 |

3.600 |

| Aコンデンサー@7GHz/イン |

0.24 |

0.240 |

0.240 |

| Aダイエル@7GHz/イン |

0.65 |

0.230 |

0.120 |

| A@7GHz/インチ |

0.89 |

0.470 |

0.360 |

| A@7GHz/30インチ |

27.00 |

14.000 |

11.000 |

| 相対コスト |

1.00 |

3.500 |

8.000 |

伝送レートが14Gb/s、伝送長が30インチの場合、Nelco4000-13SI の総伝送損失は約14dBであり、一般的なFDRチップが許容できる電圧スイング減衰は20dBから25dBの範囲であると示すことができる。したがって、この種の基板材料は、伝送距離が30インチ未満であるFDR相互接続スイッチボード設計に適用することができる。一方、FR4の総伝送減衰は約27dBであり、FR4は長距離設計のFDR設計には適用できないが、伝送距離が短いFDR相互接続インタフェースカードについては、コスト削減のためにFR4を選択することが許される。総伝送減衰が最も小さいMegtron6については、コストが最も高く、そのFDRへの適用はシステムアーキテクチャ費用の増加を招く。結論として、高周波PCB、基板材料は基本であり、基板材料の選択が信号の伝送距離を決定します。

レイアウトとスタック設計

PCB 設計では、まず回路基板の構造と層構成を考慮する必要があります。通常、回路基板のパターンと形状はすでに決定されており、層数の決定は信号周波数や回路基板のピン密度に依存します。PCB製造コスト、製造期間および信頼性要件。FDR相互接続スイッチボードは高周波・高密度であり、干渉を低減するためには多層基板の適用が不可欠なステップである。さらに、積層数の決定が極めて重要である。

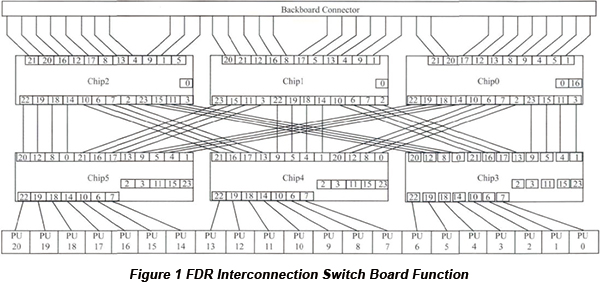

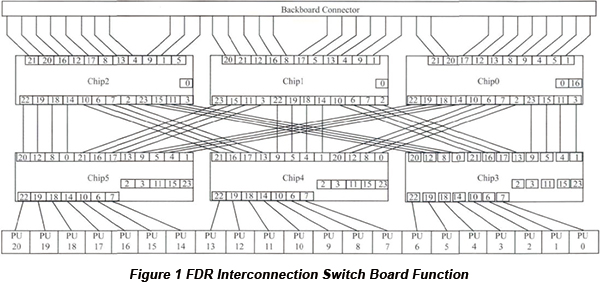

FDR相互接続チップには24個のポートがあり、各ポートは相互結合の動作方式において8チャネルのTxと8チャネルのRxを備えています。FDR相互接続ボードには6個の相互接続チップと3個のダウンリンクチップが搭載されており、32ポートがバックボードコネクタを介してアクセスされます。3個のアップリンクチップは、QSFP(Quad Small Form-factor Pluggable)光ファイバを通じて21ポートにアクセスします。アップリンクチップとダウンリンクチップは、図1に示すように4ポートを介して相互に接続されています。

FDR には、次のパッケージが含まれていますBGA(ボールグリッドアレイ)面積が50mm×50mm、ピン数が1157本、ピッチが1.0mmであり、TxおよびRxポートのP/Nピンは3つの同心円に沿って配置されている。理論的には、すべてのポートのすべてのピンをBGAの外へ引き出すために3つの信号層を適用できる。以下の2つの要素を考慮すると、2つの信号層で同心円状の一群のピンにアクセスすることができる。

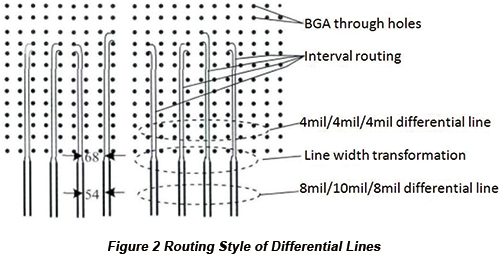

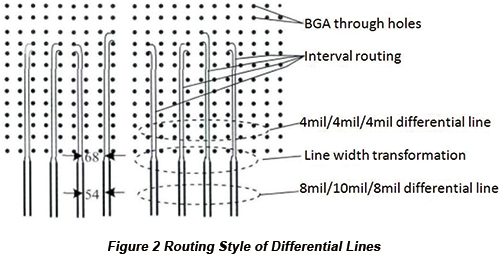

a. スペースの制約により、差動ラインの線幅/間隔/幅は 4mil/4mil/4mil となり、BGA から外に出る部分では 8mil/10mil/8mil に拡張されます。また、差動ラインペア間の距離は 50mil 以上でなければなりません。そのため、1 組の差動ラインには 2mm の幅が必要となり、最大密度のエッジ部には 48 組の信号ペアが並ぶことになります。この方法を実装するのは困難です。

b. BGAピン間のピッチは1mmです。もし同心円状の信号群にアクセスするために信号層を適用した場合、BGA直下の差動ペア間隔はわずか14milとなり、要求される50milから大きく外れてしまいます。さらに、最大並走配線長は20mmしかなく、いくらかのクロストークが発生します。

上記の否定的要因を回避するため、同心円状の信号群にアクセスする目的で 2 つの信号層が適用され、各信号層における差動信号は 50mil の間隔に従って BGA から引き出す必要があります。したがって、すべての差動信号を BGA から引き出すために、FDR 相互接続ボードには少なくとも 6 層が必要となります。ボードの接続性および配線量、さらに交換用結合コンデンサのための十分なボード面積を考慮し、8 つの内部信号層と 22 層構成が採用されています。

クロストークの解析と低減対策

クロストークは、高速かつ高密度な回路設計において最初に考慮すべき事項である。加害線路の電圧および電流が変化すると、加害線路と被害線路の間の相互容量および相互インダクタンスを介して電磁結合が生じる。被害線路に沿って伝送端子側へ流れるクロストークを近端クロストークと呼び、被害線路に沿って受信端子側へ流れるクロストークを遠端クロストークと呼ぶ。一般的に、被害線路上の総合ノイズ電圧は信号電圧の 5% 未満に抑えるべきである。その他のノイズ源および被害線路両側の加害線路を考慮したうえで、単一エッジの加害線路によるクロストークの許容値は 1% 以内に抑えるのが望ましい。

クロストーク低減に関して従うべき主なポイントは次のとおりです。

a. 攻撃側ラインと被害側ラインの間隔を広げ、並行配線の長さを短くする必要があります。

b. 統合されたグラウンドは信号のリターンパスとして用いられる。経験則によれば、50Ωのストリップラインでは、線幅の3倍の間隔を取った場合、近端クロストークはおよそ0.5%である。50Ωのマイクロストリップラインでは、線幅の3倍の間隔を取った場合、近端クロストークはおよそ1%である。ストリップラインや完全に埋め込まれたマイクロストリップラインにおける遠端クロストークはほぼゼロであり、マイクロストリップ伝送線路の遠端クロストークの極性は負で、その大きさは比較的大きい。これは、容量結合よりも誘導結合の影響が大きいためである。

・インターバルルーティング

この設計では、高速差動ラインの差動インピーダンスは 100Ω である。Si9000 フィールドソルバに基づき、ライン幅/間隔/ライン幅は 8mil/10mil/8mil と算出される。ラインが太いほど減衰は小さくなり、10mil の間隔は差動インピーダンス 100Ω を維持するためのものである。この種の差動ラインは BGA チップ領域の外側に適用される。クロストークを低減するため、本稿では 2 組の差動ライン間の間隔を 80mil 以上とする。この記事で扱うインターコネクションチップのピン間隔は 1mm であり、BGA のスルーホールサイズの制約により、BGA チップ領域内の差動ラインのライン幅/間隔/ライン幅は 4mil/4mil/4mil となる。この種の差動ラインも差動インピーダンスは 100Ω であるが、リード損失が大きいため、BGA チップ領域に入るとすぐに 4mil/4mil/4mil の差動ラインを 8mil/10mil/8mil に変換する必要がある。クロストークを低減するため、BGA チップ領域内の 4mil/4mil/4mil の差動ラインにはインターバル配線方式を適用し、2 組の差動ライン間の間隔を 50mil 以上に確保しており、その様子を図 2 に示す。

・差動ホール

この設計では、接続表面層における結合容量の付加に対応するため、専用の差動ビアが設けられている。リターンパスの逆流経路を確保するため、差動ビアのそばにはグランドビアを配置する必要がある。グランドビアを4本配置する構成が最も効果的であり、基板の面積が制限されている場合には2本のグランドビアでも対応可能である。さらに、クロストークや反射を低減するため、差動ビアに対してバックドリルや内層パッドの除去といった対策を講じ、差動ビア部でのインピーダンス変動を抑える必要がある。

・Tx と Rx が同じ層で配線されるのを防ぐ

クロストークを低減するために、Tx 差動ラインは Rx 差動ラインとは異なる層に配線する必要があります。ここで、Tx は差動ラインの送信端子を指し、Rx は差動ラインの受信端子を指します。両方を同一層に配線しなければならない場合は、安全性を確保するために、それらの間隔を 5mm 以上確保する必要があります。

・20時間ルール

高周波かつ高速なPCB回路では、RFエネルギーがPCBの電源層とグラウンド層によって結合され、電源層とグラウンド層の間でエッジ磁束漏れが発生する。無線RFエネルギーは自由空間へ放射され得る。20Hルールは、ボード上に高速電流が存在する場合、それに関連する電磁界が存在することを示している。本稿の設計では、すべての配線と基板エッジとの距離は線幅の少なくとも20倍とし、高速差動ビアと電源プレーンの分割ラインとの距離は少なくとも5mmとする。

・表層レイヤーでの配線

高周波PCBの設計においては、マイクロストリップラインとストリップライン間の比較的大きな遠端クロストークを考慮し、高速差動ラインを表層に配置することは禁止されている。本稿の設計では、製造工法の制約により、内部配線層は最大でも8層までしか使用できない。さらに、インターコネクトチップの端子配置制約により、接続ボード内の6つのチップ間のインターコネクト差動ラインの接続を、内部層のみで実現することは不可能である。

。

。 。

。