インピーダンス制御技術は、高速デジタル回路設計において非常に重要であり、高速PCBの優れた性能を確保するためには、有効な手法を採用しなければなりません。

PCB がショッピングカートに正常に追加されました

インピーダンス制御技術は、高速デジタル回路設計において非常に重要であり、高速PCBの優れた性能を確保するためには、有効な手法を採用しなければなりません。

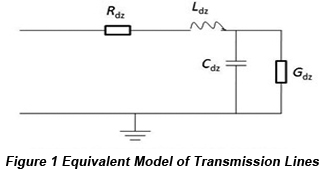

・伝送線路における等価モデル

図1は、PCB上の伝送線路の等価効果を示しており、これは直列および複数のコンデンサ、抵抗、インダクタを含む構造(RLGCモデル)である。

タンデム抵抗の一般的な値は 0.25~0.55 オーム/フィートの範囲であり、複数の抵抗器の抵抗値は通常かなり高いままです。PCB 伝送線路に寄生抵抗、寄生容量および寄生インダクタンスが加わると、伝送線路上の全体的なインピーダンスは特性インピーダンス(Z と呼ばれる)とされます。0). 特性インピーダンスの値は、線径が大きく、線が電源/グラウンドに近い、または誘電率が高い条件では比較的小さくなる。図3は長さdzの伝送線路の等価モデルを示しており、これに基づいて伝送線路の特性インピーダンスを次の式として導出できる。 この式では、L伝送線路の単位長さあたりのインダクタンスを指し、一方でC伝送線路の単位長さあたりの静電容量を指す。

この式では、L伝送線路の単位長さあたりのインダクタンスを指し、一方でC伝送線路の単位長さあたりの静電容量を指す。

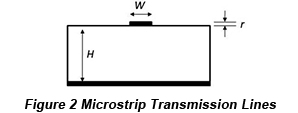

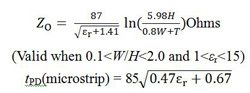

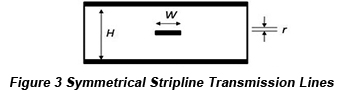

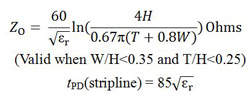

・PCB上の伝送線路のインピーダンスおよび遅延計算式

| PCB上の伝送線路 | インピーダンスおよび遅延計算式 |

|

|

|

|

上記の式において、Z0インピーダンス(オーム)を指します。W線の幅(インチ)を指しますT線の太さ(インチ)を指しますH地面までの距離(インチ)を表し、基板の相対誘電率を表します。tPDインチあたりの遅延時間(ps/inch)を指します。

・伝送線路のインピーダンス制御レイアウト規則

上記の解析に基づくと、インピーダンスおよび信号の単位遅延は信号の周波数とは無関係であり、基板構造、基板材料の比誘電率、および配線の物理的特性に関連している。この結論は理解するうえで極めて重要である。高速PCBおよび高速PCB設計に使用されます。さらに、外層の信号伝送ラインの伝送速度は内層よりもはるかに速いため、これらの要素を重要配線レイアウトの配置において考慮しなければなりません。

インピーダンス制御は、信号伝送を実現するための重要な前提条件である。しかし、伝送線路の基板構造およびインピーダンス計算式によれば、インピーダンスは~のみに依存しているPCB材料そしてPCB層構造したがって、同じ配線に対して線幅および配線仕様が変わらない場合、PCB の異なる層においてもその配線のインピーダンスは変化しません。これは、高速回路設計においては許容されないことです。

本稿では、高密度の高速PCBが設計されており、ボード上のほとんどの信号にはインピーダンス要件がある。例えば、CPCI信号ラインは65Ω、差動信号は100Ω、その他の信号はすべて50Ωでなければならない。PCB配線スペースの制約により、少なくとも10層の配線を使用する必要があり、16層のPCB設計案が採用されている。

基板全体の厚さを2mm以内に抑えなければならないため、いくつかの問題を考慮すると、積層に関していくつかの困難があります。

1).各信号層には、インピーダンスと信号品質を保護するために、それぞれに隣接したイメージプレーンが設けられています。

2).各電源プレーンには、それぞれに隣接して完全なグラウンド層が設けられているため、電源の性能が十分に確保されています。

3).ボードを積み重ねる際にはバランスが必要であり、ボードの反りを防がなければならない。

媒質の誘電率は 4.3 に設定されています。上記の積層設計に基づき、信号インピーダンスの要件を満たすため、線幅および線間距離は計算結果に従って設定する必要があります。線幅は以下の結果のように求められます。

1).表層の信号ラインの幅は 5mil で、そのインピーダンスは 58.7Ω です。

2).表層におけるCPCI信号線の幅は4.5ミルで、そのインピーダンスは61.7オームです。

3).内層の信号ラインの幅は4.5ミルで、そのインピーダンスは50.2オームです。

4).内層および表層のBGAエリアにおけるライン幅は4milであり、表層のインピーダンスは64.6Ω、内層のインピーダンスは52.7Ωです。

5).内層のマイクロストリップ差動ラインの幅は5milで、ライン間隔は6mil、インピーダンスは100.54Ωです。

6).内層のストリップライン差動配線の線幅は 4.5mil、線間距離は 10mil、インピーダンスは 96.6Ω です。

行間の間隔は次のように設定されています。

1).表層の信号線間隔(5ミル)は 5.0ミルです。

2).表層におけるCPCI信号ライン(4.5ミル)の間隔は9.0ミルです。

3).・内層の信号ライン間隔(4.5mil)は 7.0mil です。

4).表層と内層のライン間の距離は4.0ミルです。

5).内層における差動信号ライン同士の間隔、およびそれらと他の信号ラインとの間隔は、少なくとも 25mil 以上を確保する必要があります。

6).表層における差動信号ライン同士の間隔、およびそれらと他の信号ラインとの間隔は、少なくとも 20mil 以上に保つ必要があります。

後PCB印刷テストボードのインピーダンスは POLAR-Cits500 インピーダンステスターで測定され、その結果は以下の表に示す。データから、高速 PCB の設計および製造工程において、インピーダンスは 50Ω±%、60Ω±%、100Ω±% の範囲で管理しなければならないことが分かる。

| プリセットインピーダンス(Ω) | 実用インピーダンス(オーム) |

| 50 | 47.52-52.33 |

| 60 | 57.65-61.35 |

| 100 | 93.65-106.35 |

・LVDS

LVDS は、高速シリアル信号伝送レベルの一種であり、高速伝送、低消費電力、強い耐ノイズ性、長距離伝送、および容易なマッチングといった利点を備えています。LVDS の応用分野には、コンピュータ、通信、コンシューマ分野が含まれます。

・LVDS のインピーダンス設計

LVDS は電圧スイングがわずか 350mV であり、最長伝送距離は 10 メートル以上です。信号伝送の過程で、伝送線路内での反射信号によって信号が影響を受けないようにするためには、伝送線路のインピーダンスを制御し、単一線路インピーダンスを 50Ω、差動インピーダンスを 100Ω にする必要があります。実際の応用では、合理的な層構成厚みと誘電体パラメータを設定し、線幅や線間距離を調整し、さらにいくつかの高速シミュレーション解析ツールを用いて単一線路および差動線路のインピーダンスを計算することで、インピーダンスを制御することができます。

しかし、ほとんどの場合、単一線インピーダンスおよび差動インピーダンスの要件を満たすことは比較的困難です。一方で、線幅 W と線間距離 S の調整範囲は、物理的な設計スペースによって制約されます。たとえば、BGA や DIP を用いたマージンコネクタにおける配線および線幅は、パッドサイズとパッド間距離の影響を受けます。他方で、W と S の変化は、単一線および差動インピーダンスの結果に影響を及ぼします。現在では、あらかじめ設定した線幅と線間距離の関係を算出することは容易で便利になっています。

・LVDS 配線ルール

一般的に、差動信号の配線はインピーダンス設計ルールに従って実装され、これによりLVDSの品質を確保することができます。実際の配線において、LVDSは次のルールに従う必要があります。

1).差動ペアは可能な限り短くし、配線は直線的にし、スルーホールの数は減らすべきです。差動ペア内の信号線同士の間隔は一定に保たれなければなりません。これらすべてのルールは、配線の長大化や多数の折り返しを回避するのに役立ちます。折り返しについては、90度ではなく45度の折り返しを使用する必要があります。

2).ライン間のクロストークを低減するため、差動ペア間の距離は10倍以上を維持する必要があります。必要に応じて、差動ペア間のアイソレーションのためにグランドスルーホールを配置することができます。

3).LVDS は層をまたいで分割することはできません。2 本の差動信号は互いのリターンパスとなりますが、層間分割によって信号のリターンパスを遮断してはなりません。それにもかかわらず、イメージプレーンが不足していると、伝送線路はインピーダンスの不連続を引き起こす可能性があります。

4).層間での差動信号の配線は避けてください。PCB 製造時には、層間の積層位置合わせ精度は、同一層内のエッチング精度よりもはるかに低く、さらに積層時の誘電体損失も加わるため、これらすべてが差動ペア間の差動インピーダンスの変化を引き起こします。

5).インピーダンス設計では、結合方式を用いる必要があります。

6).適切なPCB積層構造を設定して、電圧レベル信号とLVDS間のアイソレーションを確保する必要があります。可能であれば、高速TTL/CMOSなどの信号は別の層に配置し、グランド層および電源層によってLVDS配線から分離します。

7).差動信号ペアは、配線の長さと整合している必要があります。

インピーダンス制御は、高速デジタル回路の設計において、高速PCBの良好な性能を確保するために非常に効果的に用いられます。線幅、層構成、および誘電率を慎重に制御することで、設計者は信号反射を最大限に低減し、信号インテグリティを維持するために必要な正しいインピーダンス値を実現できます。特にLVDS信号に対する適切な配線および設計計画は、信号の完全な伝送、信頼性、および干渉のない伝搬も保証します。

PCBCart は、高度な要求のあるアプリケーション向けに、高性能な高速 PCB の設計および製造を専門としています。最先端の技術と高度な専門知識により、正確なインピーダンス制御、高品質な PCB、そして効果的な信号伝送を実現します。最先端の生産プロセスと卓越性への情熱により、PCBCart は複雑な PCB プロジェクトにおけるお客様の最良のパートナーとなります。今すぐ PCBCart にお見積もりをご依頼いただき、高速 PCB ソリューションにおける比類のないサービスを体験してください。お客様のイノベーションと成功を加速させるために設計されたソリューションをご提供します。

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

PCBCartは、2005年以来、フルサービスのエレクトロニクス製造で卓越した品質を提供しており、高度な複雑性と高精度を要するPCBアセンブリを、多様な生産ロットに対応して専門的に手掛けています。

[email protected] [email protected]

[email protected] [email protected]

ご支援ありがとうございます!お寄せいただいたご意見は、サービス最適化のために詳細に検討させていただきます。お客様のご提案が最も価値のあるものとして採用された場合、100ドル分のクーポンを添えて、すぐにメールでご連絡いたします。