Teknologi kawalan impedans amat penting dalam reka bentuk litar digital berkelajuan tinggi, di mana kaedah yang berkesan mesti digunakan untuk memastikan prestasi PCB berkelajuan tinggi yang cemerlang.

Pengiraan Impedans dan Kawalan Impedans bagi Talian Penghantaran Litar Berkelajuan Tinggi pada PCB

• Model Setara pada Talian Penghantaran

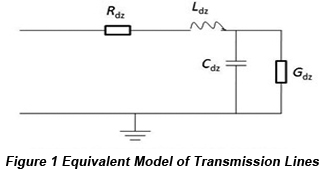

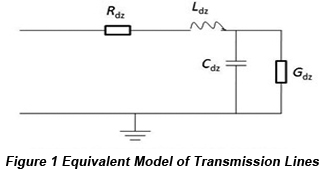

Rajah 1 menunjukkan kesan setara talian penghantaran pada PCB, iaitu satu struktur yang merangkumi susunan bersiri dan berbilang kapasitor, perintang dan induktor (model RLGC).

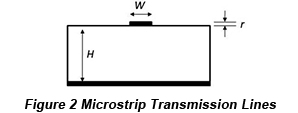

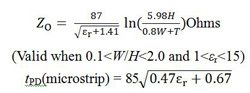

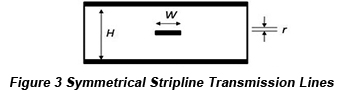

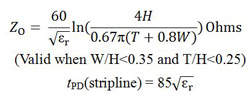

Nilai tipikal rintangan tandem adalah dalam julat dari 0.25 hingga 0.55 ohm/kaki dan nilai rintangan bagi berbilang perintang biasanya kekal agak tinggi. Dengan rintangan, kapasitans dan induktans parasit yang ditambah dalam talian penghantaran PCB, impedans keseluruhan pada talian penghantaran dirujuk sebagai impedans ciri (Z0). Nilai impedans ciri adalah agak kecil dengan syarat diameter talian adalah besar, talian hampir dengan kuasa/tanah atau pemalar dielektrik adalah tinggi. Rajah 3 menunjukkan model setara bagi talian penghantaran dengan panjang dz, berdasarkan mana impedans ciri talian penghantaran boleh dideduksikan sebagai formula: Dalam formula ini,Lmerujuk kepada induktans setiap unit panjang pada talian penghantaran sementaraCmerujuk kepada kapasitans setiap unit panjang pada talian penghantaran.

Dalam formula ini,Lmerujuk kepada induktans setiap unit panjang pada talian penghantaran sementaraCmerujuk kepada kapasitans setiap unit panjang pada talian penghantaran.

• Peraturan Susun Atur Kawalan Impedans bagi Talian Penghantaran

Berdasarkan analisis di atas, kelewatan unit bagi impedans dan isyarat tidak berkaitan dengan frekuensi isyarat tetapi berkaitan dengan struktur papan, pemalar dielektrik relatif bahan papan, dan sifat fizikal penghalaan. Kesimpulan ini amat penting untuk difahamiPCB berkelajuan tinggidan untuk reka bentuk PCB berkelajuan tinggi. Selain itu, kelajuan penghantaran talian penghantaran isyarat pada lapisan luar adalah jauh lebih pantas berbanding pada lapisan dalam, jadi unsur-unsur ini mesti diambil kira untuk susunan bentangan talian utama.

Kawalan impedans ialah premis penting untuk pelaksanaan penghantaran isyarat. Walau bagaimanapun, menurut struktur papan dan formula pengiraan impedans bagi talian penghantaran, impedans hanya bergantung kepadaBahan PCBdanStruktur lapisan PCBdengan lebar garisan dan ciri perutean yang tidak berubah untuk garisan yang sama. Oleh itu, impedans sesuatu garisan tidak akan berubah pada lapisan PCB yang berbeza, yang mana tidak dibenarkan dalam reka bentuk litar berkelajuan tinggi.

Sebuah PCB berkelajuan tinggi dengan ketumpatan tinggi direka untuk artikel ini dan kebanyakan isyarat pada papan mempunyai keperluan impedans. Sebagai contoh, talian isyarat CPCI hendaklah mempunyai impedans 65 Ohm, isyarat berbeza 100 Ohm dan semua isyarat lain masing-masing 50 Ohm. MenurutPendawaian PCBruang, sekurang-kurangnya penghalaan sepuluh lapisan mesti digunakan dan satu pelan reka bentuk PCB 16 lapisan telah ditentukan.

Oleh kerana ketebalan keseluruhan papan tidak boleh melebihi 2mm, terdapat beberapa kesukaran dari segi penyusunan dengan beberapa masalah yang perlu dipertimbangkan:

1).Setiap lapisan isyarat mempunyai satah imej bersebelahan dengannya untuk melindungi impedans dan kualiti isyarat.

2).Setiap satah kuasa mempunyai lapisan bumi lengkap di sebelahnya supaya prestasi kuasa dapat dipastikan dengan baik.

3).Penyusunan papan memerlukan keseimbangan, dengan lengkungan papan dielakkan.

Pemalar dielektrik medium ditetapkan sebagai 4.3. Berdasarkan reka bentuk susunan di atas, lebar laluan dan jarak antara laluan hendaklah ditetapkan mengikut keputusan pengiraan bagi memastikan keperluan impedans isyarat. Lebar laluan diperoleh seperti keputusan berikut:

1).Lebar talian isyarat pada lapisan permukaan ialah 5 mil dengan impedansnya 58.7 Ohm.

2).Lebar talian isyarat CPCI pada lapisan permukaan ialah 4.5 mil dengan impedansinya 61.7 Ohm.

3).Lebar talian isyarat dalam lapisan dalaman ialah 4.5 mil dengan impedansnya 50.2 Ohm.

4).Lebar garisan dalam kawasan BGA pada lapisan dalam dan lapisan permukaan ialah 4 mil dengan impedans lapisan permukaan 64.6 Ohm dan impedans lapisan dalam 52.7 Ohm.

5).Lebar talian pembeza mikrostrip dalam lapisan dalam ialah 5 mil dengan jarak antara talian 6 mil dan impedans 100.54 Ohm.

6).Lebar talian pembeza stripline dalam lapisan dalaman ialah 4.5 mil dengan jarak antara talian 10 mil dan impedans 96.6 Ohm.

Jarak antara garisan ditetapkan seperti berikut:

1).Jarak antara garisan isyarat (5 mil) pada lapisan permukaan ialah 5.0 mil.

2).Jarak antara garisan isyarat CPCI (4.5 mil) pada lapisan permukaan ialah 9.0 mil.

3).. Jarak antara garisan isyarat (4.5 mil) pada lapisan dalam ialah 7.0 mil.

4).Jarak antara garisan pada lapisan permukaan dan lapisan dalam ialah 4.0 mil.

5).Jarak antara talian isyarat pembeza pada lapisan dalam dan antara talian tersebut dengan talian isyarat lain hendaklah dikekalkan sekurang-kurangnya 25 mil.

6).Jarak antara garisan isyarat berbeza pada lapisan permukaan dan antara garisan tersebut dengan garisan isyarat lain hendaklah dikekalkan sekurang-kurangnya 20 mil.

SelepasPercetakan PCB, impedans papan ujian diuji dengan penguji impedans POLAR-Cits500 dengan keputusan seperti dalam jadual berikut. Data menunjukkan bahawa impedans mesti dikawal dalam julat 50Ohmۯ%, 60Ohmۯ% dan 100Ohmۯ% dalam proses reka bentuk dan pembuatan PCB berkelajuan tinggi.

|

Impedans Pratetap (Ohm)

|

Impedans Praktikal (Ohm)

|

| 50 |

47.52-52.33 |

| 60 |

57.65-61.35 |

| 100 |

93.65-106.35 |

LVDS dan Kawalan Impedansinya pada PCB

• LVDS

LVDS ialah sejenis aras penghantaran isyarat bersiri berkelajuan tinggi yang mempunyai kelebihan seperti kelajuan penghantaran yang tinggi, penggunaan kuasa yang rendah, keupayaan anti-gangguan yang kuat, jarak penghantaran yang jauh dan pemadanan yang mudah dilaksanakan. Bidang aplikasi LVDS merangkumi komputer, komunikasi dan penggunaan.

• Reka bentuk impedans LVDS

LVDS mempunyai ayunan voltan hanya 350 mV dengan jarak penghantaran terpanjang melebihi 10 meter. Untuk memastikan isyarat tidak dipengaruhi oleh isyarat pantulan dalam proses penghantaran isyarat pada talian penghantaran, impedans talian penghantaran mesti dikawal dengan impedans talian tunggal 50 Ohm dan impedans pembezaan 100 Ohm. Dalam aplikasi praktikal, impedans boleh dikawal dengan menetapkan ketebalan susunan lapisan dan parameter medium yang munasabah, melaraskan lebar talian dan jarak antara talian serta mengira impedans talian tunggal dan talian pembezaan dengan bantuan beberapa alat analisis simulasi berkelajuan tinggi.

Walau bagaimanapun, kebanyakan masa adalah agak sukar untuk memenuhi keperluan impedans talian tunggal dan impedans pembezaan. Dari satu segi, julat pelarasan lebar talian W dan jarak antara talian S dikawal oleh ruang reka bentuk fizikal. Sebagai contoh, penghalaan dan lebar talian pada penyambung tepi dengan BGA atau DIP dipengaruhi oleh saiz dan jarak pad. Dari segi yang lain, perubahan W dan S akan mempengaruhi keputusan impedans talian tunggal dan pembezaan. Sehingga kini, adalah mudah dan senang untuk menentukan hubungan antara lebar talian dan jarak talian yang telah ditetapkan terlebih dahulu.

• Peraturan penghalaan LVDS

Secara umumnya, penghalaan isyarat pembeza dilaksanakan mengikut peraturan reka bentuk impedans, yang mampu memastikan kualiti LVDS. Dalam penghalaan praktikal, LVDS hendaklah mematuhi peraturan berikut:

1).Pasangan pembeza hendaklah sependek yang mungkin, garisan hendaklah lurus dan bilangan lubang tembus hendaklah dikurangkan. Jarak antara garisan isyarat dalam pasangan pembeza hendaklah sama. Semua peraturan ini membantu mengelakkan pendawaian yang panjang dan banyak selekoh. Bagi selekoh, selekoh 45 darjah hendaklah digunakan dan bukannya 90 darjah.

2).Jarak antara pasangan pembeza perlu dikekalkan lebih 10 kali ganda untuk mengurangkan gangguan silang antara talian. Apabila perlu, lubang melalui bumi boleh diletakkan di antara pasangan pembeza untuk pengasingan.

3).LVDS tidak boleh dibahagikan merentasi permukaan. Walaupun dua isyarat berbeza adalah laluan kembali bersama, laluan kembali isyarat tidak boleh diputuskan akibat pembahagian merentasi permukaan. Namun begitu, talian penghantaran berkemungkinan menyebabkan ketakselanjaran impedans akibat ketiadaan satah imej.

4).Elakkan isyarat pembezaan antara lapisan. Semasa pembuatan PCB, ketepatan penjajaran susunan antara lapisan adalah jauh lebih rendah daripada ketepatan etsa dalam lapisan yang sama ditambah dengan kehilangan medium semasa penyusunan, yang semuanya membawa kepada perubahan impedans pembezaan antara pasangan pembezaan.

5).Dalam reka bentuk impedans, kaedah penggandingan harus digunakan di dalamnya.

6).Struktur susunan PCB yang sesuai harus ditetapkan untuk memastikan pengasingan antara isyarat aras voltan dan LVDS. Jika boleh, isyarat seperti TTL/CMOS berkelajuan tinggi boleh diletakkan pada lapisan yang berbeza, diasingkan daripada penghalaan LVDS oleh lapisan tanah dan kuasa.

7).Pasangan isyarat pembeza harus serasi dengan panjang penghalaan.

Kawalan impedans digunakan dengan sangat berkesan dalam mereka bentuk litar digital berkelajuan tinggi untuk memastikan prestasi yang baik bagi PCB berkelajuan tinggi. Dengan kawalan teliti ke atas lebar talian, susunan lapisan, dan pemalar dielektrik, pereka bentuk boleh mencapai aras impedans yang betul yang diperlukan untuk meminimumkan pantulan isyarat secara maksimum dan mengekalkan integriti isyarat. Perutean dan perancangan yang betul, terutamanya untuk isyarat LVDS, juga memastikan penghantaran isyarat yang sempurna, kebolehpercayaan, dan perjalanan tanpa gangguan.

PCBCart mengkhusus dalam mereka bentuk dan menghasilkan PCB berkelajuan tinggi berprestasi tinggi untuk aplikasi yang menuntut. Teknologi terkini dan kepakaran maju kami memastikan kawalan impedans yang tepat, PCB berkualiti tinggi, dan penghantaran isyarat yang berkesan. Dengan proses pengeluaran termaju dan semangat kami terhadap kecemerlangan, PCBCart ialah rakan kongsi utama anda untuk projek PCB yang kompleks. Mohon sebut harga daripada PCBCart hari ini dan alami perkhidmatan tiada tandingan dalam penyelesaian PCB berkelajuan tinggi, yang direka untuk memacu inovasi dan kejayaan anda.

Mulakan Sebut Harga Anda untuk Papan Litar Berkelajuan Tinggi

Dalam formula ini,

Dalam formula ini,