ปัจจุบัน อัตราการส่งผ่านของเครือข่ายการเชื่อมต่อระหว่างคอมพิวเตอร์ประสิทธิภาพสูงที่ใช้การส่งสัญญาณอนุกรมความเร็วสูงได้พัฒนาไปสู่ FDR (Fourteen Data Rate, 14Gb/s) ซึ่งเป็นรุ่นที่ 4 ต่อจาก SDR (Single Data Rate, 2.5Gb/s) รุ่นแรก, DDR (Double Data Rate, 5Gb/s) และ QDR (Quad Data Rate, 10Gb/s) การออกแบบ PCB (แผงวงจรพิมพ์) พร้อมด้วยการเชื่อมต่อ แผงสวิตช์ และการ์ดอินเทอร์เฟซซึ่งเป็นส่วนสำคัญต่อการก่อรูปของอินเทอร์เน็ต ได้เข้าสู่ขอบเขตความถี่สูงและความเร็วสูงระดับ FDR เนื่องจากเวลาไต่ระดับของสัญญาณ FDR ลดลงอย่างมากจนอยู่ในระดับประมาณ 10ps ทำให้ปัญหาต่าง ๆ ที่เกี่ยวข้องกับความสมบูรณ์ของสัญญาณกลายเป็นปัจจัยสำคัญในการกำหนดความเป็นไปได้ของการทำงานและการปฏิบัติงานอย่างเชื่อถือได้ เช่น การลดทอนสัญญาณ การรบกวนระหว่างสัญญาณ การสะท้อน การรบกวนทางแม่เหล็กไฟฟ้า เป็นต้น จากคุณลักษณะของชิปการเชื่อมต่อ FDR ที่มีหลายพอร์ต หลายช่องสัญญาณ หลายระดับพลังงาน และการใช้พลังงานสูง จึงมักจำเป็นต้องบูรณาการชิปการเชื่อมต่อหลายตัวไว้บนบอร์ดเชื่อมต่อเพียงแผ่นเดียวเพื่อเพิ่มอัตราการส่งผ่านข้อมูล บนบอร์ดที่มีพื้นที่จำกัด ในอีกด้านหนึ่ง จำเป็นต้องตอบสนองข้อกำหนดบางประการรวมถึงเค้าโครงคอมโพเนนต์และการกระจายความร้อน การเดินสายด้วยความหนาแน่นสูง การส่งสัญญาณระยะไกลผ่านด้านหลังของบอร์ด และความสมบูรณ์ของสัญญาณทุกชนิด อีกด้านหนึ่ง ยังต้องคำนึงถึงปัจจัยต่าง ๆ เช่น ระยะเวลาในการออกแบบ PCB ข้อจำกัดด้านเทคนิคการผลิต PCB และการควบคุมต้นทุน ดังนั้น การนำการออกแบบไปใช้จริงและการตรวจสอบด้วยการจำลองจึงเป็นเรื่องที่ยากอย่างยิ่ง โดยอ้างอิงจากตัวอย่างการออกแบบ PCB ของการเชื่อมต่อ FDR และบอร์ดสวิตช์ บทความนี้นำเสนอวิธีการปรับให้เหมาะสมในด้านการเลือกใช้วัสดุของแผ่นรองออกแบบซ้อน层กฎการกำหนดเส้นทางและการออกแบบป้องกันการรบกวนเพื่อแก้ไขปัญหาความสมบูรณ์ของสัญญาณทุกชนิดในกระบวนการออกแบบแผงวงจรพิมพ์ความเร็วสูง FDR

การเลือกคุณลักษณะการลดทอนและวัสดุแผ่นรอง

สำหรับสัญญาณความถี่สูงของ FDR การสูญเสียในสายส่งเป็นปัญหาที่เกี่ยวข้องกับความสมบูรณ์ของสัญญาณ เมื่อสัญญาณ FDR ถูกส่งจากปลายทางส่งไปยังปลายทางรับตามช่องทางการเชื่อมต่อ เนื่องจากการลดทอนความถี่สูงมีค่ามากกว่าการลดทอนความถี่ต่ำอย่างมาก รูปคลื่นของสัญญาณที่ไปถึงปลายทางรับจึงเกิดการบิดเบือนอย่างรุนแรง การบิดเบือนนี้แบ่งออกได้เป็นสองด้านหลัก ๆ คือ แอมพลิจูดแรงดันของสัญญาณลดลงอย่างมาก ในขณะที่ขอบการขึ้นของสัญญาณเสื่อมสภาพอย่างรุนแรง ด้านแรกจำกัดระยะทางการส่งของสัญญาณ ส่วนด้านหลังทำให้เกิดการรบกวนระหว่างรหัส การสูญเสียในสายส่ง A สามารถถือได้ว่าเป็นผลรวมของการสูญเสียในตัวนำAเงื่อนไขและการสูญเสียไดอิเล็กทริกAดายอิเล็กทริกดังแสดงในสูตร (1):A=Aดิล+Aเงื่อนไข.

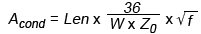

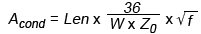

การสูญเสียตัวนำหมายถึงการสูญเสียที่เกิดจากตัวต้านทานอนุกรมบนตัวนำทองแดงระหว่างเส้นทางสัญญาณและเส้นทางกลับ ในสถานการณ์ความถี่สูง ผลสกินจะทำให้กระแสไหลที่ผิวของตัวนำทองแดงโดยรอบ เมื่อความต้านทานอนุกรมเทียบเท่าของตัวนำทองแดงเพิ่มขึ้น การสูญเสียตัวนำจะเพิ่มขึ้นตามความถี่ที่เพิ่มขึ้น ซึ่งแปรผันตามรากที่สองของความถี่ ดังที่แสดงในสมการ (2): .

.

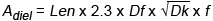

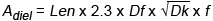

การสูญเสียไดอิเล็กทริกหมายถึงการสูญเสียที่เกิดจากตัวกลางของวัสดุแผ่นรอง ซึ่งถูกกำหนดโดยคุณสมบัติของวัสดุเป็นหลัก และไม่เกี่ยวข้องกับโครงสร้างทางเรขาคณิตรวมถึงความกว้างของตัวนำ โดยมีความแปรผันตามความถี่ในเชิงสัดส่วนโดยตรง ซึ่งแสดงดังในสมการ (3): .

.

จากสมการ (2) การเพิ่มความกว้างของลายวงจรสามารถลดการสูญเสียของตัวนำได้ อย่างไรก็ตาม ในทางปฏิบัติการออกแบบแผงวงจรพิมพ์ความกว้างของตัวนำไม่สามารถกว้างได้อย่างไม่จำกัด เนื่องจากข้อจำกัดของระยะห่างระหว่างขา บอร์ด จำนวนเลเยอร์สัญญาณ และอิมพีแดนซ์ ความกว้าง/ระยะห่าง/ความกว้างของตัวนำที่ใช้กันโดยทั่วไปในการออกแบบ FDR มักจะเป็น 7mil/7mil/7mil หรือ 8mil/10mil/8mil เมื่อความกว้างของตัวนำเท่ากัน การสูญเสียของตัวนำจะแปรผันตามความยาวของตัวนำโดยตรง โดยไม่เกี่ยวข้องกับวัสดุ ดังนั้น เพื่อให้ลดการสูญเสียการส่งสัญญาณโดยรวม จึงต้องพิจารณาเฉพาะการสูญเสียไดอิเล็กทริกเท่านั้น จากสมการ (3) การสูญเสียไดอิเล็กทริกจะแปรผันตามแฟกเตอร์การสูญเสีย และการใช้วัสดุที่มีแฟกเตอร์การสูญเสียต่ำจะช่วยลดการสูญเสียไดอิเล็กทริก ส่งผลให้การสูญเสียการส่งสัญญาณโดยรวมลดลง

ตารางที่ 1 แสดงพารามิเตอร์คุณลักษณะของวัสดุบอร์ดความเร็วสูงทั่วไปสามชนิด และค่าการสูญเสียที่คำนวณตามสมการ (1), (2) และ (3) เมื่ออัตราการส่งข้อมูลเท่ากับ 14Gb/s ความกว้างตัวนำ 8mil และอิมพีแดนซ์ 50Ω

|

พารามิเตอร์วัสดุบอร์ด

|

FR4

|

Nelco4000-13SI

|

Megtron6

|

| Df@10GHz |

0.02 |

0.008 |

0.004 |

| Dk@10GHz |

4.10 |

3.200 |

3.600 |

| Aเงื่อนไข@7GHz/ใน |

0.24 |

0.240 |

0.240 |

| Aดิล@7GHz/ใน |

0.65 |

0.230 |

0.120 |

| A@7GHz/นิ้ว |

0.89 |

0.470 |

0.360 |

| A@7GHz/30นิ้ว |

27.00 |

14.000 |

11.000 |

| ต้นทุนสัมพัทธ์ |

1.00 |

3.500 |

8.000 |

สามารถระบุได้ว่า เมื่ออัตราการส่งข้อมูลเท่ากับ 14Gb/s และความยาวการส่งเท่ากับ 30 นิ้ว การสูญเสียการส่งสัญญาณโดยรวมของ Nelco4000-13SI อยู่ที่ประมาณ 14dB ในขณะที่การลดทอนแอมพลิจูดของสวิงแรงดันที่ชิป FDR ทั่วไปสามารถทนได้อยู่ในช่วง 20dB ถึง 25dB ดังนั้น วัสดุบอร์ดประเภทนี้จึงสามารถนำมาใช้ในการออกแบบบอร์ดสวิตช์การเชื่อมต่อ FDR ที่มีระยะการส่งสัญญาณน้อยกว่า 30 นิ้วได้ อย่างไรก็ตาม การลดทอนการส่งสัญญาณโดยรวมของ FR4 อยู่ที่ประมาณ 27dB และ FR4 ไม่สามารถนำมาใช้สำหรับการออกแบบ FDR ที่มีระยะทางไกลได้ แต่การ์ดอินเทอร์เฟซการเชื่อมต่อ FDR ที่มีระยะการส่งสัญญาณสั้นสามารถเลือกใช้ FR4 เพื่อลดต้นทุนได้ สำหรับ Megtron6 ซึ่งมีการลดทอนการส่งสัญญาณโดยรวมต่ำที่สุดนั้น มีต้นทุนสูงที่สุด และการนำไปใช้ใน FDR จะทำให้ค่าธรรมเนียมด้านสถาปัตยกรรมระบบเพิ่มขึ้น สรุปแล้ว สำหรับแผงวงจรพิมพ์ความถี่สูงวัสดุบอร์ดเป็นพื้นฐาน และการเลือกวัสดุบอร์ดจะเป็นตัวกำหนดความยาวการส่งสัญญาณ

การออกแบบเลย์เอาต์และสแต็ก

สำหรับการออกแบบ PCB โครงสร้างและสแต็กของแผงวงจรต้องได้รับการพิจารณาเป็นอันดับแรก โดยทั่วไปแล้ว ลวดลายและรูปทรงของแผงวงจรจะถูกกำหนดไว้ล่วงหน้า และการกำหนดจำนวนชั้นของสแต็กนั้นขึ้นอยู่กับความถี่ของสัญญาณ ความหนาแน่นของขาพินบนแผงวงจรต้นทุนการผลิตแผงวงจรพิมพ์ช่วงเวลาการผลิตและข้อกำหนดด้านความเชื่อถือได้ แผงสวิตช์เชื่อมต่อ FDR มีความถี่และความหนาแน่นสูง และการใช้แผงวงจรหลายชั้นเป็นขั้นตอนที่จำเป็นในการลดสัญญาณรบกวน นอกจากนี้ การกำหนดจำนวนชั้นของการซ้อนแผงวงจรยังมีความสำคัญอย่างยิ่ง

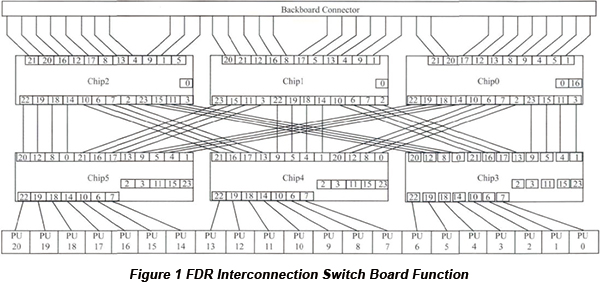

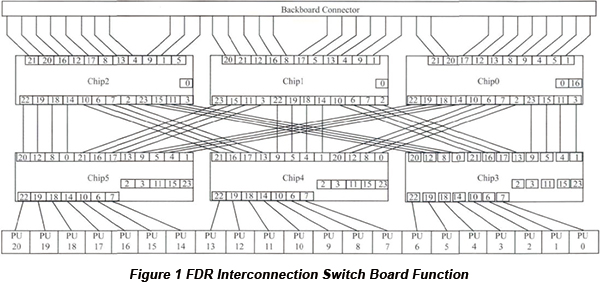

ชิปเชื่อมต่อ FDR มีพอร์ตทั้งหมด 24 พอร์ต และแต่ละพอร์ตมีช่องสัญญาณส่ง (Tx) 8 ช่องและช่องสัญญาณรับ (Rx) 8 ช่อง โดยทำงานในโหมดการเชื่อมต่อแบบประสานกัน บอร์ดเชื่อมต่อ FDR ใช้ชิปเชื่อมต่อ 6 ชิปและชิปดาวน์ลิงก์ 3 ชิป และเข้าถึงได้ 32 พอร์ตผ่านคอนเน็กเตอร์ของแผงหลัง ชิปอัปลิงก์ 3 ชิปเข้าถึง 21 พอร์ตผ่านสายใยแก้วนำแสง QSFP (Quad Small Form-factor Pluggable) ชิปอัปลิงก์และชิปดาวน์ลิงก์เชื่อมต่อถึงกันผ่าน 4 พอร์ต ดังแสดงในรูปที่ 1

FDR มีแพ็กเกจของBGA (บอลกริดอาร์เรย์)มีพื้นที่ขนาด 50 มม. x 50 มม. จำนวนพิน 1157 พิน ระยะห่าง 1.0 มม. และพิน P/N ที่พอร์ตของ Tx และ Rx ถูกจัดเรียงตามวงกลมร่วมศูนย์ 3 วง ตามทฤษฎีแล้ว สามารถใช้เลเยอร์สัญญาณ 3 เลเยอร์เพื่อนำพินทั้งหมดที่พอร์ตทั้งหมดออกจาก BGA ได้ โดยเมื่อพิจารณาสองปัจจัยต่อไปนี้ สามารถใช้เลเยอร์สัญญาณเพียงสองเลเยอร์ในการเข้าถึงกลุ่มพินของวงกลมร่วมศูนย์ได้

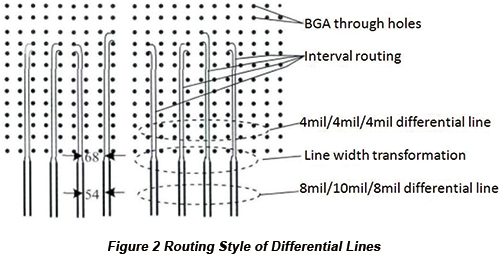

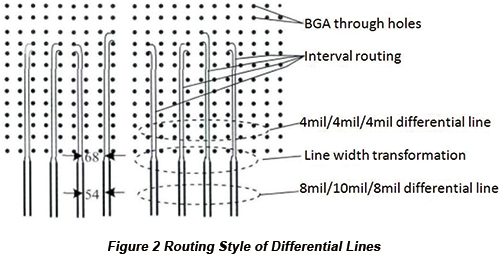

a. เนื่องจากข้อจำกัดด้านระยะห่าง ความกว้างของลาย/ระยะห่าง/ความกว้างของลายดิฟเฟอเรนเชียลคือ 4mil/4mil/4mil และจะขยายเป็น 8mil/10mil/8mil เมื่อออกจาก BGA และระยะห่างระหว่างคู่ลายดิฟเฟอเรนเชียลต้องไม่น้อยกว่า 50mil ดังนั้น คู่ลายดิฟเฟอเรนเชียลหนึ่งคู่จึงต้องใช้ความกว้าง 2 มม. และมีสัญญาณ 48 คู่ตามแนวขอบที่มีความหนาแน่นสูงสุด จึงทำให้วิธีนี้ยากต่อการใช้งาน

b. ระยะห่างระหว่างขา BGA คือ 1 มม. หากใช้เลเยอร์สัญญาณเพื่อเข้าถึงกลุ่มสัญญาณแบบวงกลมร่วมศูนย์ ระยะห่างระหว่างคู่สายดิฟเฟอเรนเชียลใต้ BGA จะมีเพียง 14 mil ซึ่งห่างไกลจากค่าที่ต้องการคือ 50 mil นอกจากนี้ ความยาวการเดินสายแบบขนานสูงสุดมีเพียง 20 มม. ซึ่งจะก่อให้เกิดครอสทอล์กบางส่วน

เพื่อหลีกเลี่ยงปัจจัยด้านลบที่กล่าวถึงข้างต้น มีการใช้เลเยอร์สัญญาณสองชั้นเพื่อเข้าถึงกลุ่มสัญญาณวงกลมร่วมศูนย์ และสัญญาณดิฟเฟอเรนเชียลในแต่ละเลเยอร์สัญญาณจะต้องถูกนำออกจาก BGA ตามระยะห่าง 50 mil ดังนั้น บอร์ดการเชื่อมต่อ FDR จึงต้องใช้เลเยอร์อย่างน้อย 6 ชั้นเพื่อให้สัญญาณดิฟเฟอเรนเชียลทั้งหมดถูกนำออกจาก BGA เมื่อพิจารณาถึงการเชื่อมต่อและปริมาณการเดินลายของบอร์ด รวมถึงพื้นที่ผิวบอร์ดที่เพียงพอสำหรับตัวเก็บประจุคัปปลิงแบบแลกเปลี่ยน จึงมีการใช้สัญญาณภายใน 8 เลเยอร์ และโครงสร้างซ้อนเลเยอร์ 22 ชั้น

การวิเคราะห์การรบกวนระหว่างสัญญาณและมาตรการลดทอน

ครอสทอล์กเป็นปัจจัยแรกที่ต้องพิจารณาในการออกแบบวงจรความเร็วสูงและความหนาแน่นสูง เมื่อแรงดันไฟฟ้าและกระแสไฟฟ้าในสายรบกวนมีการเปลี่ยนแปลง จะเกิดการคัปปลิงทางแม่เหล็กไฟฟ้าผ่านความจุประจุร่วมและการเหนี่ยวนำร่วมระหว่างสายรบกวนและสายเหยื่อ ครอสทอล์กที่ไหลไปทางด้านขั้วส่งตามแนวสายเหยื่อเรียกว่าครอสทอล์กปลายใกล้ ในขณะที่ครอสทอล์กที่ไหลไปทางด้านขั้วรับตามแนวสายเหยื่อเรียกว่าครอสทอล์กปลายไกล โดยทั่วไปแล้ว แรงดันรบกวนรวมบนสายเหยื่อควรถูกควบคุมให้น้อยกว่า 5% ของแรงดันสัญญาณ โดยดีที่สุดคือควบคุมงบประมาณครอสทอล์กของสายรบกวนขอบสัญญาณเดี่ยวให้อยู่ภายใน 1% โดยคำนึงถึงแหล่งกำเนิดสัญญาณรบกวนอื่น ๆ และสายรบกวนที่อยู่รอบ ๆ ทั้งสองด้านของสายเหยื่อด้วย

ประเด็นสำคัญที่ต้องปฏิบัติตามในด้านการลดการรบกวนระหว่างสัญญาณ ได้แก่:

a. ควรเพิ่มระยะห่างระหว่างสายรบกวนกับสายที่ถูกรบกวน และลดความยาวของการเดินสายแบบขนาน

b. กราวด์แบบรวมถูกใช้เป็นเส้นทางกลับของสัญญาณ ตามกฎเชิงประจักษ์ สำหรับสตริปลายน์ที่มีอิมพีแดนซ์ 50Ω เมื่อระยะห่างเท่ากับสามเท่าของความกว้างลายทองแดง ครอสทอล์กใกล้ต้นทางจะมีค่าประมาณ 0.5% สำหรับไมโครสตริปลายน์ที่มีอิมพีแดนซ์ 50Ω เมื่อระยะห่างเท่ากับสามเท่าของความกว้างลายทองแดง ครอสทอล์กใกล้ต้นทางจะมีค่าประมาณ 1% ครอสทอล์กปลายทางบนสตริปลายน์หรือไมโครสตริปลายน์แบบฝังเต็มนั้นแทบจะเป็นศูนย์ และขั้วของครอสทอล์กปลายทางในไมโครสตริปทรานส์มิสชันไลน์จะเป็นลบ โดยมีขนาดค่อนข้างมาก เนื่องจากอิทธิพลของการคัปปลิงแบบอุปนัยมีมากกว่าการคัปปลิงแบบตัวเก็บประจุ

• การกำหนดเส้นทางแบบช่วง

ในการออกแบบนี้ อิมพีแดนซ์เชิงต่างศักย์ของไลน์ความเร็วสูงแบบดิฟเฟอเรนเชียลคือ 100Ω โดยอ้างอิงจากตัวแก้สมการเชิงสนาม Si9000 ได้คำนวณให้ความกว้าง/ระยะห่าง/ความกว้างของลายทองแดงเป็น 8mil/10mil/8mil ยิ่งลายทองแดงกว้าง การลดทอนสัญญาณยิ่งน้อย และระยะห่าง 10mil ใช้เพื่อคงอิมพีแดนซ์เชิงต่างศักย์ที่ 100Ω ไลน์ดิฟเฟอเรนเชียลชนิดนี้ถูกใช้นอกบริเวณชิป BGA เพื่อให้ครอสทอล์กลดลง ระยะห่างระหว่างคู่ไลน์ดิฟเฟอเรนเชียลสองคู่ต้องไม่น้อยกว่า 80mil ระยะห่างระหว่างขาของชิปเชื่อมต่อในบทความนี้คือ 1mm และข้อจำกัดขนาดรูทะลุของ BGA ทำให้ความกว้าง/ระยะห่าง/ความกว้างของไลน์ดิฟเฟอเรนเชียลในบริเวณชิป BGA เป็น 4mil/4mil/4mil แม้อิมพีแดนซ์เชิงต่างศักย์ของไลน์ดิฟเฟอเรนเชียลชนิดนี้จะเป็น 100Ω เช่นกัน แต่การสูญเสียที่ลีดมีค่าสูง จึงต้องแปลงไลน์ดิฟเฟอเรนเชียล 4mil/4mil/4mil ให้เป็น 8mil/10mil/8mil ทันทีที่เข้าสู่บริเวณชิป BGA เพื่อให้ครอสทอล์กลดลง ไลน์ดิฟเฟอเรนเชียล 4mil/4mil/4mil ในบริเวณชิป BGA ใช้วิธีการเดินลายแบบเว้นช่วง เพื่อให้แน่ใจว่าระยะห่างระหว่างคู่ไลน์ดิฟเฟอเรนเชียลสองคู่มากกว่า 50mil เช่นกัน ดังแสดงในรูปที่ 2

• รูต่างระดับ

มีการกำหนดรูดิฟเฟอเรนเชียลเฉพาะในดีไซน์นี้เพื่อใช้สำหรับการประยุกต์ใช้คาปาซิแตนซ์แบบแลกเปลี่ยนคัปปลิงบนชั้นผิวหน้าของการเชื่อมต่อ ต้องวางรูกราวด์ไว้ข้างรูดิฟเฟอเรนเชียลเพื่อจัดให้มีช่องทางกระแสย้อนกลับสำหรับเส้นทางกลับ การออกแบบให้มีรูกราวด์สี่รูให้ผลลัพธ์ที่ดีที่สุด และสามารถใช้เพียงสองรูได้เมื่อพื้นที่ของบอร์ดมีจำกัด นอกจากนี้ ควรใช้มาตรการต่าง ๆ เช่น การเจาะย้อน (back drilling) และการตัดแผ่นแพดด้านในออกกับรูดิฟเฟอเรนเชียล เพื่อลดการเปลี่ยนแปลงอิมพีแดนซ์ที่รูดิฟเฟอเรนเชียล เพื่อลดครอสทอล์กและการสะท้อนกลับ

• ป้องกันไม่ให้ Tx และ Rx ถูกจัดเส้นทางอยู่ในเลเยอร์เดียวกัน

เพื่อเป็นการลดสัญญาณรบกวนแบบครอสทอล์ก ควรจัดวางเส้นลายสัญญาณดิฟเฟอเรนเชียลของ Tx ให้อยู่คนละเลเยอร์กับเส้นลายสัญญาณดิฟเฟอเรนเชียลของ Rx โดยที่ Tx หมายถึงขั้วต้นทางของเส้นลายสัญญาณดิฟเฟอเรนเชียล ส่วน Rx หมายถึงขั้วปลายทางที่รับสัญญาณของเส้นลายสัญญาณดิฟเฟอเรนเชียล หากจำเป็นต้องจัดวางทั้งสองให้อยู่ในเลเยอร์เดียวกัน ระยะห่างระหว่างกันจะต้องมากกว่า 5 มม. เพื่อความปลอดภัย

• กฎ 20 ชั่วโมง

ในวงจร PCB ที่มีความถี่สูงและความเร็วสูง พลังงาน RF จะถูกคัปปลิงผ่านชั้นจ่ายไฟและชั้นกราวด์ของ PCB และเกิดการรั่วไหลของฟลักซ์แม่เหล็กบริเวณขอบระหว่างชั้นจ่ายไฟและชั้นกราวด์ พลังงาน RF แบบคลื่นวิทยุสามารถแผ่รังสีออกสู่พื้นที่อิสระได้ กฎ 20H ระบุว่า หากมีการไหลของกระแสความเร็วสูงบนบอร์ด จะมีสนามแม่เหล็กไฟฟ้าที่เกี่ยวข้องเกิดขึ้น ในการออกแบบของบทความนี้ ระยะห่างระหว่างลายวงจรทั้งหมดกับขอบบอร์ดควรมีอย่างน้อย 20 เท่าของความกว้างลายวงจร และระยะห่างระหว่างรูดิฟเฟอเรนเชียลความเร็วสูงกับเส้นตัดแบ่งระนาบจ่ายไฟควรมีอย่างน้อย 5 มม.

• การกำหนดเส้นทางบนชั้นผิว

ในการออกแบบแผ่นวงจรพิมพ์ความถี่สูง (High-frequency PCB) เมื่อพิจารณาถึงการเกิดครอสทอล์กปลายไกล (far-end crosstalk) ที่ค่อนข้างมากระหว่างไมโครสตริปไลน์และสตริปไลน์ จึงห้ามวางลายวงจรดิฟเฟอเรนเชียลความเร็วสูงบนเลเยอร์ผิวหน้า ในการออกแบบของบทความนี้ ต้องใช้เลเยอร์เดินลายภายในได้มากที่สุดเพียง 8 เลเยอร์เนื่องจากข้อจำกัดของกระบวนการผลิต นอกจากนี้ ข้อจำกัดด้านการจัดเรียงขาเทอร์มินัลของชิปอินเตอร์คอนเน็กต์ยังทำให้ไม่สามารถใช้เฉพาะเลเยอร์ภายในในการเชื่อมต่อสัญญาณดิฟเฟอเรนเชียลของอินเตอร์คอนเน็กต์ระหว่างชิปทั้ง 6 ตัวภายในบอร์ดเชื่อมต่อได้

.

. .

.