In der schnelllebigen Elektronikbranche ist die damit verbundene Komplexitätmehrlagige LeiterplatteDesign ist das, was benötigt wird, um die Methoden in Bezug auf die Leistung und Haltbarkeit der aktuellen Geräte zuverlässig und effektiv zu machen. DerLagenaufbau, das eine Hauptkomponente dieses Designprozesses ist, ist entscheidend für das Management elektromagnetischer Störungen (EMI). Obwohl ein gut durchdachter PCB-Stackup dazu beitragen kann, die EMI-Leistung zu verbessern sowieSignalintegritäteine schlecht umgesetzte Lagenaufbau-Konfiguration kann sie erheblich beeinträchtigen. In diesem Beitrag wird die komplexe Verbindung zwischen dem Lagenaufbau und der EMI-Leistung untersucht und es werden Lösungen für die Aufgabe vorgestellt, Ihre PCB-Designs zu optimieren, um eine bessere EMI-Leistung zu erzielen.

Die Komplexität des PCB-Lagenaufbaus

In einem mehrlagigen Lagenaufbau werden verschiedene Schichten aus leitfähigem und isolierendem Material übereinandergestapelt, darunter: Signallagen,Masseflächenund Stromversorgungsebenen. Dieses Design wird anhand der elektrischen, mechanischen und thermischen Anforderungen der Anwendung ausgewählt. Typische Stackup-Designs sind 4-Lagen-, 6-Lagen- und 8-Lagen-Leiterplatten, obwohl der Stackup mit zunehmender Geschwindigkeit und Dichte der Anwendungen an Komplexität abnimmt.

Der Lagenaufbau hat einen starken Einfluss auf Signalpfade, Leistungszuweisung und die Abschirmung der Leiterplatte gegen unerwünschte elektromagnetische Signalwechselwirkungen. Ohne eine ordnungsgemäße Auslegung des Lagenaufbaus,Übersprechenkönnen Probleme mit der Signalintegrität und die Unfähigkeit, die gesetzlichen EMI-Vorschriften einzuhalten, auftreten. Um eine wirksame EMI-Abschirmung und die Zuverlässigkeit Ihres Produkts im realen Einsatzszenario zu erreichen, ist es entscheidend, Ihren mehrlagigen PCB-Stackup zu optimieren.

Der Einfluss des Lagenaufbaus auf die EMI-Leistung

Eine Reihe wichtiger Elemente im Lagenaufbau beeinflusst die EMI-Leistung. Ein Verständnis dieser Elemente kann dazu beitragen, die Anfälligkeit für EMI zu verringern und die Einhaltung der EMV-Normen sicherzustellen.

Nähe von Masseflächen

Masseflächen können als Referenzpunkt für Signale verwendet werden und bieten Abschirmung gegen EMI. Wenn Signallagen in der Nähe einer Massefläche angeordnet sind, verkürzt sich der Rückstrompfad des Hochfrequenzsignals, was die Schleifenfläche und die abgestrahlten Signale verringert. Ein standardmäßiger 4-Lagen-Aufbau würde Signallagen neben Masseflächen platzieren und damit im Wesentlichen die Impedanz reduzieren und zugleich die EMI-Kontrolle verbessern.

Kopplung zwischen Strom- und Masseflächen

Die natürliche kapazitive Schicht, die durch die Nähe zwischen Versorgungs- und Masseflächen entsteht, ist entscheidend für die Entkopplung von Hochfrequenzrauschen. Die Verwendung dieser Strategie kann einer Leiterplatte Spannungsstabilität und Rauschreduzierung verschaffen, indem sie einen niederimpedanten Rückstrompfad bereitstellt. Bei einem 6-Lagen-Aufbau verbessert die Anordnung von Versorgungs- und Masseflächen in den inneren Lagen die Rauschunterdrückung und die EMV-Eigenschaften.

Stackup-Symmetrie

Ein symmetrischer Lagenaufbau ist nicht nur in Bezug auf die strukturelle Integrität wichtig, sondern auch für eine gleichmäßige EMV-Leistung. Gleiche Signal-, Versorgungs- und Masselagen tragen zur Aufrechterhaltung einer konstanten Impedanz sowie zur Reduzierung von EMV bei. Ein Beispiel ist ein 8-lagiger Lagenaufbau, bei dem sich Signal- und Masselagen abwechseln. Das bedeutet, dass jede Signallage von den Vorteilen einer Masseführung in einer direkt angrenzenden Lage profitiert, was zu einer idealen Abschirmung gegen EMV führt.

Optimierungsstrategien für den Lagenaufbau zur EMV-Leistung

Wenn Designer die Auswirkungen des Lagenaufbaus auf die elektromagnetische Verträglichkeit (EMV) kennen, können sie wirksame Methoden zur Reduzierung von Störungen und zur Verbesserung der Leistung einsetzen.

Priorisieren Sie die enge Platzierung von Signal und Masse

Bei Hochgeschwindigkeitssignalen sollten Masseflächen benachbart zu Signallagen positioniert werden, um die Induktivität zu verringern und elektromagnetische Felder zu isolieren. Zwischen diesen Leitern können deutlich dünnere Dielektrikschichten die abgestrahlte EMI drastisch reduzieren, wobei eine kontrollierte Impedanz häufig im Bereich von 50 Ohm liegt.

Exklusive Stromversorgungs- und Masseflächen

Eigene Masse- und Versorgungsebenen sind notwendig, um eine gute EMI-Reduktion zu erreichen. Geteilte Ebenen sollten nicht unnötig aufgetrennt werden, da dies EMI-Hotspots verursachen kann. Fügen Sie Entkopplungskondensatoren um die Versorgungspins der ICs herum hinzu, um Rauschen zu reduzieren.

Abstand zwischen Schichten optimieren

Ein verringerter Abstand zwischen Strom- und Masseebenen erhöht die Kapazität, was Rauschen unterdrückt. Verwenden Sie Impedanzrechner, um die optimale Dielektrikdicke für Hochgeschwindigkeitsdesigns zu bestimmen.

Minimieren Sie Signal-Lagenkreuzungen

Verwenden Sie weniger Vias, um die Kontinuität des Rückstrompfads sicherzustellen und EMI zu minimieren. Falls es sich nicht vermeiden lässt, platzieren Sie Stitching-Vias, die mit Masse verbunden sind, nahe an den Signal-Vias, um eine kleine Schleifenfläche zu gewährleisten.

Empfindliche Signale abschirmen

Das Platzieren empfindlicher Analog- oder HF-Signale zwischen Masseebenen erzeugt einen Faraday-Käfig-Effekt, der den Schutz vor äußerer Störeinwirkung verbessert.

Häufige Fehler und wie man sie vermeidet

Selbst bei gut gemeintem Stackup-Design können einige Fehler die EMI-Leistung beeinträchtigen. Fragmentierte Masseflächen sollten vermieden werden, da sie Rückstrompfade stören, und die Platzierung der Versorgungsebenen sollte so gewählt werden, dass ein geringer Abstand zur Masseebene besteht, was zur Erhöhung des Entkopplungseffekts beiträgt. Achten Sie außerdem auf die Belegung der Signallagen, um Übersprechen und EMI zu reduzieren.

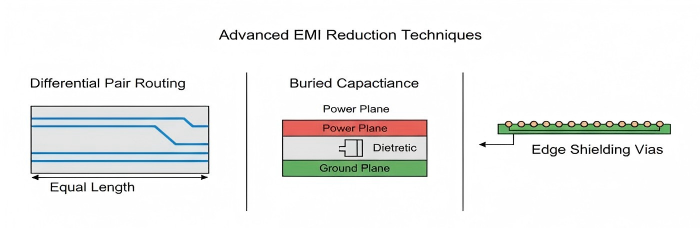

Fortgeschrittene Hochleistungs-EMI-Reduktionstechniken

Komplexere Methoden zur Reduzierung von EMI in sehr anspruchsvollen Designs umfassen eingebrachte Kapazität, undDifferenzialpaar-Routing. Verwenden Sie Kantenschirmung an Masse-Vias und führen Sie Leitungen stets paarweise, um Störungen fernzuhalten.

Angesichts der sich rasant entwickelnden Elektronikwelt ist es wichtig, die Feinheiten des Designs von mehrlagigen Leiterplatten (PCBs) zu beherrschen, um die Zuverlässigkeit und Leistungsfähigkeit moderner Geräte zu gewährleisten. Der Lagenaufbau ist ein grundlegendes Element dieses Designprozesses und spielt eine entscheidende Rolle bei der Beherrschung elektromagnetischer Störungen (EMI). Während ein gut geplanter PCB-Lagenaufbau die EMI-Eigenschaften verbessern und die Signalintegrität sicherstellen kann, kann ein schlecht umgesetzter Lagenaufbau diese drastisch verschlechtern. Dieses Papier behandelt das komplexe Zusammenspiel zwischen Lagenaufbau und EMI-Leistung und gibt Hinweise darauf, wie Sie all Ihre PCB-Designs nutzen können, um eine bessere EMI-Performance zu erreichen.

Um eine hochwertige Leiterplattenlösung zu erreichen, die sowohl im EMV-Management als auch in der Gesamtleistung effektiv ist, lohnt sich eine Partnerschaft mit PCBCart. PCBCart verfügt über jahrelange Erfahrung und den Anspruch auf Exzellenz, weshalb wir die neuesten Technologien in der Fertigungsindustrie bereitstellen können und Ihnen helfen, sicherzustellen, dass Ihre Designs den Branchenstandards entsprechen. Wir verstehen die Bedeutung des PCB-Stackups und führen personalisierte Programme durch, um Ihre Designs mit EMV-Management zum Laufen zu bringen. Fordern Sie ein Angebot bei PCBCart an und finden Sie heraus, wie wir Ihre innovativen Ideen mit Präzision und Zuverlässigkeit Wirklichkeit werden lassen können.

Erhalten Sie ein Sofortangebot für die fortschrittliche mehrlagige Leiterplattenbestückung

Hilfreiche Ressourcen

•Designregeln für die Leiterplattenaufteilung zur Verbesserung der EMV

•Drei Designaspekte zur Sicherstellung der EMV von Laptop‑Leiterplatten

•Hochgeschwindigkeits‑Leiterplatten‑Routingtechniken zur Reduzierung des Einflusses von EMI

•Elemente, die den charakteristischen Wellenwiderstand von Leiterplatten beeinflussen, und Lösungen

•Probleme bei der Anwendung der EMV-Technologie im PCB-Design und entsprechende Strategien

•Überlegungen zum Antennendesign im IoT-Design