急速に発展するエレクトロニクス業界において、関与する複雑さは多層PCBデザインとは、現在のガジェットの性能と耐久性に関して、その手法を信頼性が高く効果的なものにするために必要とされるものである。レイヤースタックアップこれは、この設計プロセスの主要な要素であり、電磁干渉(EMI)管理において極めて重要である。十分に検討されたPCBスタックアップは、EMI性能の向上に役立つだけでなく、シグナルインテグリティ不適切に実装されたスタックアップは、その性能を大きく損なう可能性があります。本稿では、層構成(レイヤースタックアップ)とEMI性能との複雑な関係を検証し、より良いEMI性能を達成するためにPCB設計を最適化する手法について解説します。

PCB層構成の複雑さ

多層スタックアップでは、導電性および絶縁性の異なる層が積み重ねられ、これには信号層が含まれます。グラウンドプレーンおよび電源プレーン。この設計は、アプリケーションの電気的、機械的および熱的要件に基づいて選択される。一般的なスタックアップ設計は4層、6層および8層基板であるが、高速かつ高密度なアプリケーションが求められるにつれて、スタックアップは複雑さが低減される。

スタックアップは、信号経路、電源配分、および不要な電磁信号干渉から基板を遮蔽することに強い影響を及ぼします。スタックアップが適切に設計されていないと、クロストーク、信号インテグリティの問題や、規制上のEMI要件に適合できない事態が発生する可能性があります。実際の使用環境において効果的なEMIシールドと製品の信頼性を確保するためには、多層PCBスタックアップを最適化することが極めて重要です。

レイヤースタックアップがEMI性能に与える影響

スタックアップ内のいくつかの重要な要素は、EMI の性能に影響を与えます。これらについて深く理解することで、EMI に対する脆弱性を低減し、EMC 規格への適合を確保することができます。

グラウンドプレーンの近接度

グラウンドプレーンは信号の基準点として使用でき、EMI に対するシールドを提供します。信号層をグラウンドプレーンの近くに配置すると、高周波信号のリターンパスが短くなり、ループ面積と放射信号が低減されます。標準的な 4 層スタックアップでは、信号層はグラウンドプレーンに隣接して配置され、その結果としてインピーダンスが実質的に低減され、EMI 制御も向上します。

電源プレーンとグラウンドプレーン間の結合

電源プレーンとグラウンドプレーンが近接することで形成される自然な容量性層は、高周波ノイズのデカップリングにおいて極めて重要である。この手法を用いることで、基板に電圧の安定性とノイズ低減をもたらし、リターン電流に対して低インピーダンスの経路を提供できる。6層スタックアップでは、電源プレーンとグラウンドプレーンを中間層に配置することで、ノイズ低減とEMI性能が向上する。

スタックアップの対称性

対称スタックアップは構造的な完全性の観点で重要であるだけでなく、均一なEMI性能の観点でも重要です。等しい数の信号層、電源層、およびグラウンド層は、一貫したインピーダンスの維持とEMIの低減に寄与します。例えば、信号層とグラウンド層が交互に配置された8層スタックアップでは、すべての信号層が、直近の隣接層の一つにグラウンドを持つ利点を享受でき、その結果、理想的なEMIシールドが実現されます。

EMI性能向上のためのスタックアップ最適化戦略

スタックアップがEMIに及ぼす影響を理解していれば、設計者は干渉を低減し性能を向上させるための有効な手法を用いることができる。

クローズドシグナルとグラウンドの配置を優先する

高速信号においては、インダクタンスを低減し電磁界を遮蔽するために、信号層に隣接してグラウンドプレーンを配置する必要があります。これらの導体間に、はるかに薄い誘電体層を設けることで放射EMIを大幅に低減でき、インピーダンスはしばしば50オーム程度に制御されます。

専用の電源プレーンとグラウンドプレーン

良好なEMI低減を実現するためには、専用のグラウンドプレーンと電源プレーンが必要です。不要な場合にプレーンを分割する必要はありません。これはEMIホットスポットを引き起こす可能性があるためです。ノイズを低減するために、ICの電源ピンの周囲にデカップリングコンデンサを追加してください。

レイヤー間隔の最適化

電源プレーンとグラウンドプレーン間の距離を縮めると、容量が増加し、ノイズが抑制されます。インピーダンス計算ツールを使用して、高速設計で使用する最適な誘電体厚さを求めてください。

信号層の交差を最小限に抑える

リターンパスの連続性を確保し、EMI を最小限に抑えるために、ビアの使用数を減らしてください。どうしても回避できない場合は、ループ面積を小さく保つために、信号ビアの近くにグラウンドに接続されたスティッチングビアを配置してください。

機密信号を保護する

繊細なアナログ信号やRF信号をグラウンドプレーンの間に配置すると、ファラデーケージ効果が得られ、外部からの干渉に対する保護が向上します。

よくある間違いとその回避方法

スタックアップ設計が善意に基づいて適切に行われていても、いくつかの誤りがEMI性能に影響を及ぼす可能性があります。分割されたグラウンドプレーンは、リターンパスを乱すため避けるべきであり、デカップリング効果を高めるために、グラウンドプレーンとの距離を近く保てるよう電源プレーンの配置を適切に行う必要があります。また、クロストークとEMIを低減するために、信号層への負荷にも注意してください。

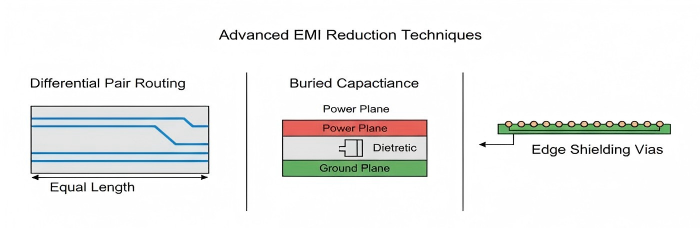

先進的高性能EMI低減技術

非常に複雑な設計においてEMIを低減するための、より高度な手法には、埋め込みキャパシタンスや差動ペアルーティング・グランドビアにはエッジシールドを使用し、常にペア配線を行ってノイズを抑えること。

急速に進化するエレクトロニクスの世界において、現代のデバイスの信頼性と性能を保証するためには、多層PCB設計の複雑さを習得することが重要です。レイヤースタックアップはこの設計プロセスの基本要素であり、電磁干渉(EMI)の管理において重要な役割を果たします。綿密に計画されたPCBスタックアップはEMI特性を改善し、信号の完全性を保証できますが、不適切に実装されたスタックアップはそれらを著しく悪化させる可能性があります。本稿では、レイヤースタックアップとEMI性能との間に存在する複雑な相互作用について論じるとともに、あらゆるPCB設計においてより良いEMI性能を達成するためのヒントを提示します。

高いレベルのEMI対策と総合的な性能を備えた優れたPCBソリューションを実現するためには、PCBCartとの提携を検討する価値があります。PCBCartは長年の経験と卓越性を追求する姿勢を持っており、そのおかげで、最新の製造技術を提供し、お客様の設計が業界標準を満たすことを支援できます。私たちはPCBスタックアップの重要性を理解しており、お客様の設計がEMI対策に適合するよう、個別化されたプログラムを運用しています。PCBCartに見積もりをご依頼いただき、私たちがどのように高い精度と信頼性をもってお客様の革新的なアイデアを実現できるかをご確認ください。

役立つリソース

・EMC向上のためのPCB分割設計ルール

•ノートパソコン用PCBのEMCを確保するための3つの設計上の考慮事項

•EMIの影響を低減するための高速PCB配線技術

•PCBの特性インピーダンスに影響を与える要素とその対策

•PCB設計におけるEMC技術応用の問題点と対策

•IoT設計におけるアンテナ設計の考慮事項